Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:02.

- Nazadnje spremenjeno 2025-01-23 15:08.

JDM je priljubljen programer PIC, ker uporablja serijska vrata, minimalne komponente in ne potrebuje napajanja. Toda tam je zmeda, s številnimi različicami programerjev na internetu, katere delujejo s katerimi PIC? V tem "navodilu" smo preizkusili JDM in pokazal sem, kako simulirati vezje s pomočjo Spice, ki bo odgovorila na vsa vaša vprašanja!

Zaloge

LTspice, ki ga lahko prenesete iz Analog Devices tukaj.

Tukaj potrebujete tudi datoteke vezja JDM.

1. korak: Zahteve za serijska vrata

JDM zahteva serijska vrata, ki ustrezajo specifikacijam EIA232, v idealnem primeru z napetostjo +12/-12.

Po podatkovnem listu Texas Instruments Line Driver MC1488 (slika 3)

Izhodna impedanca = 4V/8mA = 500 ohmov

Omejitev toka kratkega stika = 12mV, brez časovne omejitve - brez poškodb čipa.

Priporočena vhodna impedanca linijskega sprejemnika = 3 k do 7 k ohmov.

Zaporedna vrata na starejših namiznih računalnikih uporabljajo +12v/-12V, ki izpolnjujejo to zahtevo.

Zaporedna vrata na novejših prenosnih računalnikih uporabljajo nižje napetosti. JDM lahko deluje ali pa tudi ne - odgovor je bolj zapleten.

2. korak: Zahteve glede programiranja PIC

Informacije o zahtevah glede programiranja PIC so pridobljene pri Microchipu. Zgornje je za tipično napravo.

3. korak: Specifikacija JDM

Ali se je prvotno spletno mesto JDM v megli časa izgubilo? Tako lahko ugibamo, kaj je oblikovalec prvotno nameraval za specifikacijo.

- Zagotovite VDD = 5 V in največ IDD = 2 mA (za različico "v vtičnici")

- Zagotovite VHH = 13V in največ do IHH = največ 0,2 mA.

- MCLR Čas dviga tVHHR = 1uS max.

- Različica ICSP mora biti sposobna potegniti MCLR nizko proti 22 k vlečenju na tarčo.

4. korak: Opis vezja

Slika JDM1 temelji na "standardnem" vezju JDM, vzetem s spletnega mesta PICPgm. To je programer "PIC in Socket", kjer PIC napaja iz zatičev TX in RTS. Prvotni diagram je bilo težko razumeti, zato sem ga prerisal po običajni konvenciji tokovnega toka od zgoraj navzdol. Dodal sem tudi LED indikatorje “RESET”, “PROG” in “RTS”, ki so potrebni med gradnjo in preskušanjem. Upajmo, da to nima škodljivega vpliva na vedenje.

Običajna konvencija o načrtovanju vezja je skupna vsem osnovam, ključna značilnost JDM pa je, da je masa serijskih vrat (GND) povezana z VDD. To povzroča zmedo, saj se signali serijskih vrat merijo glede na signale GND, PIC glede na logično maso (VSS).

Ko je TX visok, se Q1 obnaša kot dve naprej usmerjeni diodi. (Zbiralec Q1 ni obratno pristranski kot pri normalnem delovanju tranzistorja). Zbiralnik Q1 napolni C2, ki ga pri VDD+8V vpne Zener (D3). Oddajnik Q1 oddaja 13V na MCLR za način programa/preverjanja.

Ko se TX zniža, se kondenzator C3 napolni skozi D1, VSS pa na VDD-5V vpelje zener (D5). Tudi TX je pritrjen na (VSS-0,6) z D1. Q1 je izklopljen, C1 zadrži polnjenje za naslednji programski impulz. MCLR je pritrjen na 0V z D2, zato je PIC ponastavljen.

Ko je RTS visok, se ura pošlje na PGC. D4 objemka PGC pri logiki VDD visoko. Ko je RTS nizek, se kondenzator C3 napolni skozi D6, VSS pa se pri VDD-5V vpelje z zenerjem (D5). D6 vpenja PGC pri VSS ali logiki 0.

Med programiranjem se podatki, poslani na DTR, berejo na PGD, ki ga PIC konfigurira kot vhod. Ko je DTR visok, Q2 deluje kot "sledilnik oddajnika" in je napetost PGD približno (VDD-0,6) ali logika 1. Ko je DTR nizek, deluje Q2 kot slab tranzistor (obrnjeni oddajniki in kolektorski zatiči). Q2 nizko potegne PGD, ki ga D7 vpne pri VSS ali logiki 0.

Med preverjanjem PIC konfigurira PGD kot izhod za pošiljanje podatkov na serijska vrata. DTR mora biti nastavljen visoko, podatki pa se berejo v sistemu CTS. Ko je izhod PGD visok, je Q2 izklopljen, CTS = DTR = +12V. Ko je izhod PGD nizek, je Q2 vklopljen. Zbiralec Q2 črpa tok (12V+5V)/(1k+1k5) = 7mA iz DTR in potegne CTS nizko, do VSS.

5. korak: Pripravite se na simulacijo

Prenesite LT spice, shranite in odprite datoteke vezja (*.asc), ki so na voljo tukaj. Za simulacijo vezja mu moramo dati nekaj vhodov, nato pa "slediti" izhodom. V1, V2 V3 simulirajo 12V serijska vrata z izhodno impedanco R11, R12, R13.

- V1 generira 2 programska impulza na TX od 0,5 ms do 4,5 ms

- V2 generira niz podatkovnih impulzov na DTR od 1,5 do 4,5 ms

- V3 generira rafal urnih impulzov na RTS od 0,5 do 3,5 ms

Vse komponente V4, X1, R15 in R16 so del simulacije.

- V4 generira 2 impulza od 2,5 do 4,5 ms za preverjanje podatkov.

- Jumper X1 simulira OUTPUT na PGD.

- R15, R16 simulirajo "nalaganje" PIC na VDD in MCLR.

6. korak: Spremembe ICSP

Slika JDM3 prikazuje različico programiranja "v vezju". Spremembe izvirnika so

- Vtičnico ZIF zamenjajte s priključkom ICSP.

- PIC se zdaj napaja z napajanjem v ciljno vezje (V5).

- Odstranite 5V zener (D5).

- Mali kondenzator 100pF (C4) se premakne poleg PIC na ciljnem vezju.

- LED diode napajajo iz vezja, kjer je to mogoče.

- Na ciljnem vezju sta potrebna vlečni upor MCLR (R10) in dioda (D10).

- OPOZORILO. Ciljna plošča mora imeti "plavajoče" napajanje, najbolje baterijo.

- Ne priključujte ciljnega ozemljitve (VSS) na ozemljitev računalnika/osebnega računalnika tako, da hkrati z JDM priključite katera koli druga vrata računalnika.

Po simulaciji JDM1 se je pojavil problem dolgega časa polnjenja na C2. Potem se po branju Fruttenboela zdi, da sta bila C2 in Q1 dodana kot sprememba izvirnika. Ne morem misliti, kaj nameravata storiti C2 in Q1, razen ustvarjanja težav. Zato se za JDM4 vrnemo k starejši zasnovi Fruttenboela, ki je preprosta in razumljiva. D1 in D3/LED2 objemka MCLR med VSS in VDD+8V. Vrednost R1 se zmanjša na 3k3, kar je dovolj za osvetlitev LED2 pri 12V.

JDM4 je zasnovan tudi za delo s šibkejšimi serijskimi vrati. Ko je TX visok (+9V), je vir toka TX = (9-8)/(1k +3k3) = 0,2 ma, ravno toliko, da MCLR potegne visoko, čeprav ne zadostuje za osvetlitev LED2. Ko je TX nizek (približno -7V), je tok TX = (9-7)/1k = 2mA. LED1 tok = (7-2 za led)/(2k7) = 1,8 mA. MCLR izvlečni tok = 7-5,5/3k3 = 0,5 mA.

To vezje je bilo tudi preizkušeno (simulacija JDM5), da bi ugotovili, kaj se zgodi s serijskimi vrati +/- 7V minimum, kjer ni dovolj napetosti za vzdrževanje VHH = 13V. Namen C1 je zdaj očiten, C1 ustvari kratko +ve povečanje MCLR, 33us konico na naraščajočem robu TX, dovolj dolgo, da PIC morda vstopi v programski način? Odstranite mostiček X2 (onemogočite LED1), ker ni dovolj toka, da bi MCLR potegnil nizko in osvetlil LED1 skupaj. Ko se TX zniža, je tok TX = (7V-5.5V)/(1k+3k3) = 0.3mA, kar je dovolj, da MCLR potegnemo nizko proti vlečnemu R10.

7. korak: Rezultati simulacije

Če si želite ogledati grafične datoteke, je bolje, da z desno miškino tipko kliknete spodnje povezave in nato izberete "Odpri povezavo v novem zavihku"

Simulacija 1: sled MCLR, VSS in RTS za izvirni JDM1. Takoj so opazna opazovanja 1, 2 in 3.

Simulacija 2: sled MCLR in VSS ter RTS za spremenjeni JDM2, ki odpravlja prejšnje težave.

Simulacija 3: sled PGD, VSS in PGC za pošiljanje podatkov JDM2 v programskem načinu. Opazovanje 4 pri 3,5 mS.

Simulacija 4: sled PGD, VSS in CTS za JDM2 v načinu preverjanja (vstavljen mostiček X1). v redu

Simulacija 5: sled MCLR, VSS, PGD in PGC za JDM3. ICSP z napajanjem iz vezja reši številne težave.

Simulacija 6: sled MCLR, VSS, PGD in PGC za JDM4 z +/- 9V zaporednimi vrati. MCLR se takoj dvigne in popolnoma deluje.

Simulacija 7: sled MCLR, VSS in TX za JDM5 z odstranjenimi zaporednimi vrati +/- 7V in mostičem X2. C1 ustvarja +ve povečanje (konico) na naraščajočem robu MCLR, kar je približno dovolj, da MCLR potisne nad TX na 13V.

8. korak: Zaključki

Spice res dobro razkriva "skrite skrivnosti" delovanja vezja. Očitno vezje JDM deluje in je združljivo z mnogimi čipi PIC, vendar naslednja opažanja razkrivajo možne omejitve/težave z združljivostjo/napake?

- Dolg čas porasta MCLR, medtem ko se C2 ob prvem impulzu TX napolni do VPP. Napaka specifikacije 3.

- Serijska vrata zaračunajo C2, ko je TX visok, RTS pa nizka. Toda RTS ima tudi nalogo polnjenja C3. Ko se oba pojavita hkrati, to ustvari večjo obremenitev za RTS, zato C3 pri simulaciji izgubi naboj (VSS naraste) pri 2 ms. Napaka specifikacije 1.

- C3 izgubi naboj (VSS začne naraščati), ko se impulzi ure ustavijo pri 3,5 ms.

- Kakšen je namen C2, je sploh potreben?

Rešitve

- Domnevno PICPgm uporablja programsko opremo "krog". Za prednapolnitev na C2 mora uporabiti dolg impulz TX, nato pa šele po drugem impulzu TX vstopi v način programiranja? Za simulacijo sem znižal vrednost C2 na 1uF, da bi dal čas vzpona 1ms. Ni idealna rešitev.

- C2 in C3 razdelite tako, da se polnijo neodvisno. Ena majhna sprememba JDM2, C2 se nanaša na GND namesto na VSS.

- Rešuje JDM3. ICSP je veliko bolj zanesljiv, saj PIC napaja ciljno vezje.

- JDM4 rešuje problem 1. To je preprosta zasnova, ki popolnoma odpravlja C2.

9. korak: In končno

Dokaz pudinga je v prehranjevanju. Ta JDM deluje, zato ga uporabljajte še naprej.

In moja priporočila so:

- uporabite JDM2 za programiranje vtičnic in 12V serijska vrata,

- uporabite JDM4 za programer ICSP in serijska vrata nad +/- 9 V,

- uporabite JDM4 z odstranjenim mostičkom X2 za serijska vrata nad +/- 7V.

Reference:

Začimba Analog Devices LT

picpgm

Fruttenboel

Spremljajte več projektov PIC na sly-cornerju

Priporočena:

Rentgenski pregled BGA- Naučite se pregledati?: 7 korakov

Rentgenski pregled BGA-Naučite se pregledati ?: Ta navodila vam bodo predstavila, kako pripraviti uporabo in 2D rentgenski sistem za pregled BGA, ter nekaj namigov, na kaj morate biti pozorni pri opravljanju rentgenskega pregleda BGA. potrebovali boste: rentgenski sistem, ki lahko drži zapestni trak PCBPCBESD smockESD

Kako utripati ali programirati vdelano programsko opremo ESP8266 AT z uporabo bliskavice ESP8266 in programerja, modul IOT Wifi: 6 korakov

Kako utripati ali programirati vdelano programsko opremo ESP8266 AT z uporabo bliskavice in programerja ESP8266, modula IOT Wifi: Opis: Ta modul je adapter /programer USB za module ESP8266 tipa ESP-01 ali ESP-01S. Za priključitev ESP01 je priročno opremljen z žensko glavo 2x4P 2,54 mm. Prav tako prekine vse zatiče ESP-01 preko 2x4P 2,54 mm moškega h

Več programerja ATtiny85/13A: 6 korakov

Več programerjev ATtiny85/13A: Ste že kdaj naredili projekt, kot je "LDR x Arduino UNO Automatic Light" ali podoben, ki uporablja samo 2-3 digitalna V/I vhoda vašega 32-polnega mikrokrmilnika? V redu je, če samo delate nekaj izdelava prototipov, kaj pa, če želite dokončati ali izdelati

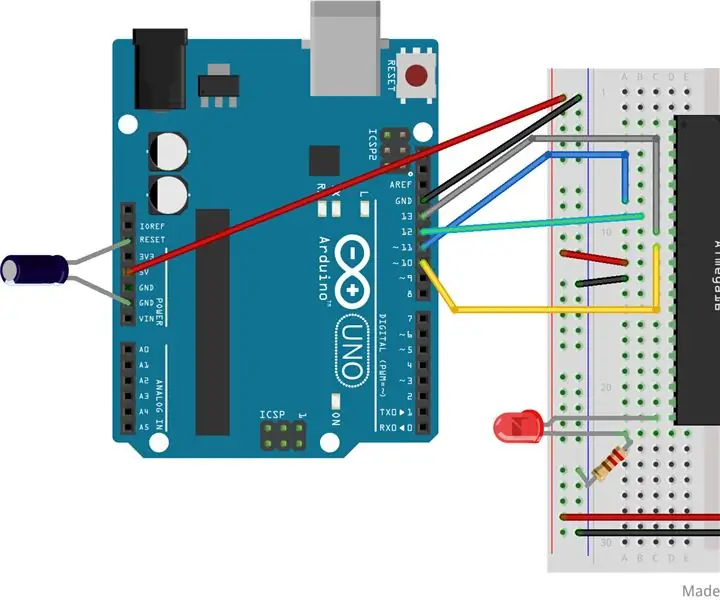

Kako naložiti kodo C v ِ AVR z uporabo programa Arduino Uno kot programerja: 6 korakov

Kako naložiti C kodo v ِ AVR z uporabo Arduino Uno kot programerja: Pozdravljeni vsi: D Tukaj bom predstavil preprost način programiranja katerega koli čipa AVR z uporabo Arduino Uno R3 Vse, kar morate zapisati v svoj mikrokrmilnik, je Arduino Uno, namesto da kupite določeno programer, ki stane veliko

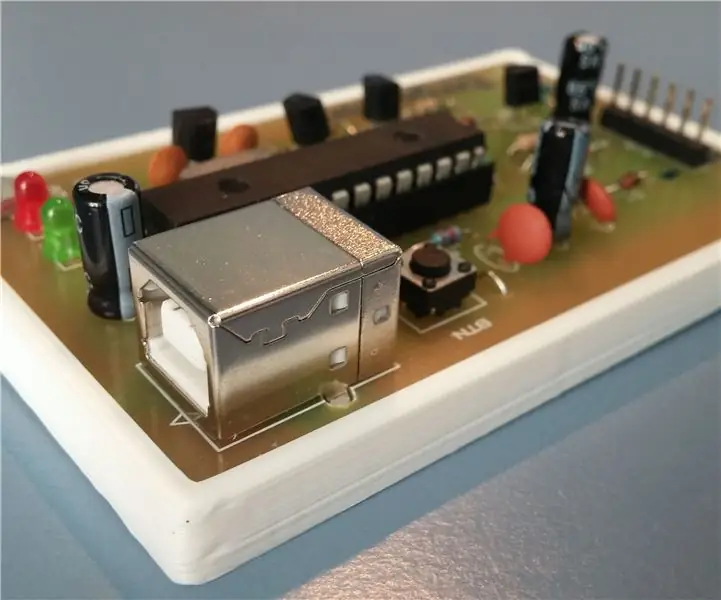

Kako narediti programerja PIC - PicKit 2 'klon': 4 koraki (s slikami)

Kako narediti programerja PIC - PicKit 2 'klon': Pozdravljeni! To je kratek Navodilo za izdelavo programerja PIC, ki deluje kot PicKit 2. To sem naredil, ker je veliko cenejši od nakupa izvirnega PicKita in ker Microchip, proizvajalci mikrokrmilnikov PIC in programer PicKit, pr