Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:04.

- Nazadnje spremenjeno 2025-01-23 15:08.

Presenečen sem nad takšnimi odzivi, ki jih dobim na tem blogu. Hvala, fantje, ki ste obiskali moj blog in me spodbudili, da svoje znanje delim z vami. Tokrat bom predstavil zasnovo drugega zanimivega modula, ki ga vidimo v vseh SOC -jih - Interrupt Controller.

Oblikovali bomo preprost, a zmogljiv programirljiv krmilnik prekinitev. To je popolnoma nastavljiva in parametrizirana zasnova, ki je prenosljiva na različnih platformah. To sem zasnoval, potem ko sem veliko bral o nekaterih priljubljenih arhitekturah krmilnikov prekinitev, kot so NVIC, 8259a, RISC-V PLIC, Microblaze's INTC itd. Upam, da vam bo ta blog koristen in vam bo pomagal razumeti, kako procesorji obravnavajo prekinitve s pomočjo krmilnika prekinitev.

1. korak: Specifikacije

Naslednje specifikacije IP:

- AHB3-Lite vmesnik.

-

Statistično nastavljivi parametri:

- Št. Zunanjih virov prekinitev; podpira do 63 prekinitev.

- Število prednostnih ravni; podpira do 63 stopenj.

- Število ravni gnezdenja; podpira do 8 ravni gnezdenja.

- Širina vodila; 32 ali 64.

- Globalno in lokalno maskirane prekinitve.

- Dinamično nastavljiva raven prioritete za vsak prekinitev.

- Dva načina delovanja - način popolnoma ugnezden in način enake prioritete.

- Podpira aktivne občutljive prekinitve na visoki ravni.

Pri oblikovanju se uporablja mehanizem prekinitve rokovanja, ki ga navdihujejo specifikacije RISC-V PLIC.

Preprečenost prekinitve je navdihnjena z 8259a

Drugi odčitki: Microblaze INTC, NVIC

2. korak: Pregled PIC

Programabilni krmilnik prekinitev (PIC) sprejema več prekinitev od zunanjih zunanjih naprav in jih združi v en sam izhod prekinitve do ciljnega procesorskega jedra.

PIC se nadzoruje prek kontrolnih in statusnih registrov. Vsi registri PIC so preslikani v pomnilnik in so dostopni prek vmesnika vodila AHB3-Lite.

Banko registrov sestavljajo konfiguracijski register, registri za omogočanje, čakajoči registri, registri za uporabo, registri prioritet in register ID, ki so značilni za krmilnike prekinitev.

Konfiguracijski register se uporablja za nastavitev načina delovanja PIC. Deluje lahko v popolnoma ugnezdenem načinu ali v načinu enake prioritete.

Vsakemu prekinitvi je mogoče dodeliti prioritete in jih individualno prikriti. Podprto je tudi globalno prikrivanje vseh prekinitev.

Banka registrov sodeluje s programom Priority Resolver in BTC (Binary-Tree-Comparator), da razreši prioritete čakajočih prekinitev in ustrezno potrdi prekinitev procesorju. Register ID vsebuje ID najvišje prioritetne čakajoče prekinitve.

3. korak: Oblikovanje in izvedba RTL

Oblikovanje PIC poudarja zmanjšanje zamud pri reševanju prednostnih nalog, kar je časovno najbolj kritičen del zasnove. Ker zasnova rešuje prioritete v enem ciklu, se zmogljivost poslabša s povečanjem števila virov s kompleksnostjo Log2.

Zasnova je bila uspešno izvedena in časovno preverjen čas do naslednjih frekvenc na FPGA-jih Artix-7.

- Do 15 virov: 100 MHz

- Do 63 virov: 50 MHz

Zakasnitev prekinitve, ki jo doda samo PIC, so 3 cikli ure (brez časa preklopa konteksta procesorja in prvega časa pridobivanja navodil ISR).

4. korak: Pomembne opombe in priložene datoteke

Pomembne opombe:

- Če je vmesnik AHB3-Lite nezaželen, lahko spremenite zgornji modul in uporabite okostje PIC. Na voljo je preskusna miza za IP z vmesnikom AHB3-Lite.

- PIC IP v1.0 je popolnoma prenosna, gola RTL zasnova.

- Funkcionalno preverjeno za delo v obeh načinih.

Priložene datoteke:

- Oblikovalske kode in testna miza v VHDL.

- Celotna dokumentacija IP.

To je odprtokodna zasnova … Uporabite jo lahko …

Za vsa vprašanja in kadar koli:

Mitu Raj

Priporočena:

Oblikovanje preprostega štirismernega sklopa krmilnika pridruženega predpomnilnika v VHDL: 4 koraki

Oblikovanje preprostega štirismernega nabora krmilnika pridruženega predpomnilnika v VHDL: V mojem prejšnjem navodilu smo videli, kako oblikovati preprost krmilnik predpomnilnika z neposrednim preslikavo. Tokrat gremo korak naprej. Oblikovali bomo preprost štirismerno nastavljen asociativni krmilnik predpomnilnika. Prednost? Manjša stopnja zamud, a za ceno perfo

Zasnova enostavnega krmilnika predpomnilnika v VHDL: 4 koraki

Oblikovanje enostavnega krmilnika predpomnilnika v VHDL: Pišem to navodilo, ker se mi je zdelo malo težko pridobiti referenčno kodo VHDL, da bi se naučili in začeli oblikovati krmilnik predpomnilnika. Zato sem sam iz nič oblikoval krmilnik predpomnilnika in ga uspešno preizkusil na FPGA. Imam p

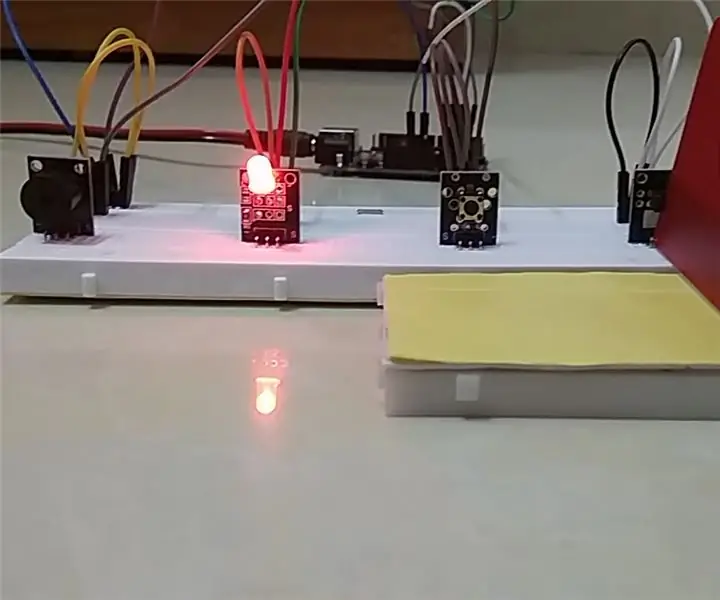

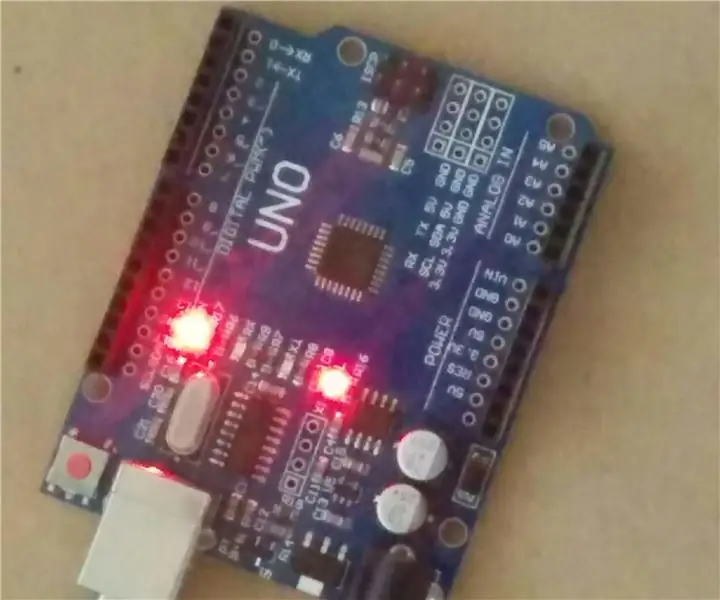

Arduino senzor za blokiranje svetlobe (modul za prekinitev fotografij) - varovanje kartic na varnem (prototip): 4 koraki

Arduino senzor za blokiranje svetlobe (modul za prekinitev fotografij) - Varovanje vaših kartic na varnem (prototip): Ta projekt je prototip in v tem projektu bom razpravljal o tem, kako lahko hranite svoje kartice - kot so kreditne kartice, debetne kartice, darilne kartice - varno. Oglejte si zgornje slike, da vidite, kako ta projekt deluje. Dovolite mi, da si ogledam

Zasnova enostavnega krmilnika VGA v VHDL in Verilogu: 5 korakov

Oblikovanje preprostega krmilnika VGA v VHDL in Verilogu: V tem navodilu bomo zasnovali preprost krmilnik VGA v RTL. VGA krmilnik je digitalno vezje, zasnovano za pogon zaslonov VGA. Bere iz pomnilnika okvirja (pomnilnik VGA), ki predstavlja okvir za prikaz, in ustvari naslednje

Arduino - periodični prekinitev: 4 koraki

Arduino - Periodic Interrupt: Ta Instructable govori o uporabi periodičnih prekinitev za merjenje časa v programih Arduino. To je korak za nadobudnega programerja Arduina, ki ve, da lahko Arduino naredi več, vendar ne ve, kako to uresničiti. Če obstaja performans pr