Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:04.

- Nazadnje spremenjeno 2025-01-23 15:08.

V mojem prejšnjem navodilu smo videli, kako oblikovati preprost krmilnik predpomnilnika z neposrednim preslikavo. Tokrat gremo korak naprej. Oblikovali bomo preprost štirismerno nastavljen asociativni krmilnik predpomnilnika. Prednost? Manj zamud, vendar za ceno zmogljivosti. Tako kot v mojem prejšnjem blogu bi oblikovali in posnemali celoten procesor, glavni pomnilnik in okolje predpomnilnika za preizkus našega krmilnika predpomnilnika. Upam, da se vam bo to zdelo koristno za razumevanje konceptov in oblikovanje lastnih krmilnikov predpomnilnika v prihodnosti. Ker sta model za procesor (testna miza) in glavni pomnilniški sistem popolnoma enaka mojemu prejšnjemu blogu, jih ne bom več razlagal. Za podrobnosti o tem glejte prejšnja navodila.

1. korak: Specifikacije

Hitro si oglejte specifikacije Cache Controller -ja, predstavljene tukaj:

- Štirismerni krmilnik pridruženega predpomnilnika (pojdite na to povezavo, če iščete krmilnik predpomnilnika z neposrednim preslikavo).

- Blokiranje predpomnilnika z eno banko.

- Politika pisanja o zadetkih pri pisanju.

- Politika pisanja okoli napak pri pisanju.

- Politika zamenjave drevesnega psevdo-LRU (pLRU).

- Označite matriko v krmilniku.

- Nastavljivi parametri.

Privzete specifikacije za predpomnilnik in glavni pomnilnik so enake kot v prejšnjih navodilih. Obrnite se nanje.

2. korak: RTL pogled na celoten sistem

Celotna RTL predstavitev zgornjega modula je prikazana na sliki (brez procesorja). Privzete specifikacije za avtobuse so:

- Vsi podatkovni avtobusi so 32-bitni.

- Address Bus = 32-bitno vodilo (Toda pomnilnik naslavlja le 10 bitov).

- Podatkovni blok = 128 bitov (širokopasovna vodila za branje).

- Vse komponente poganja ista ura.

3. korak: Rezultati testa

Zgornji modul je bil preizkušen s testno mizo, ki preprosto modelira procesor brez cevovoda, tako kot smo to storili v zadnjem navodilu. Testna miza pogosto ustvarja zahteve za branje/pisanje podatkov v pomnilnik. To se posmehuje tipičnim navodilom "Naloži" in "Shrani", ki so skupni v vseh programih, ki jih izvaja procesor.

Rezultati preskusa so uspešno preverili funkcionalnost krmilnika predpomnilnika. Sledi statistika preskusov:

- Vsi signali za branje/pisanje Miss in Hit so bili pravilno ustvarjeni.

- Vse operacije branja/pisanja podatkov so bile uspešne na vse štiri načine.

- Algoritem pLRU je uspešno preverjen za zamenjavo vrstic predpomnilnika.

- Neodkritih/nedoslednih podatkov ni bilo zaznanih.

- Oblikovanje je bilo časovno uspešno preverjeno za Maxm. Ura Frekvenca delovanja = 100 MHz na plošči Xilinx Virtex-4 ML-403 (celoten sistem), 110 MHz samo za krmilnik predpomnilnika.

- Za glavni pomnilnik so sklepali na blokovske RAM -e. Vsi drugi nizi so bili izvedeni na LUT.

4. korak: Priložene datoteke

Temu blogu so tukaj priložene naslednje datoteke:

- . VHD datoteke Cache Controller, Cache Data Array, Main Memory System.

- Testna klop.

- Dokumentacija o krmilniku predpomnilnika.

Opombe:

- Poglejte dokumentacijo za popolno razumevanje specifikacij krmilnika predpomnilnika, predstavljenih tukaj.

- Vse spremembe kode so odvisne od drugih modulov. Zato je treba spremembe opraviti preudarno.

- Bodite pozorni na vse komentarje in naslove, ki sem jih podal.

- Če iz kakršnega koli razloga za glavni pomnilnik ne sklepate blok RAM -a, ZMANJŠAJTE velikost pomnilnika, čemur sledijo spremembe širine naslovnega vodila po datotekah itd. Tako, da je isti pomnilnik mogoče implementirati bodisi v LUT ali v porazdeljeni RAM. Tako boste prihranili čas in sredstva. Ali pa pojdite na posebno dokumentacijo FPGA in poiščite združljivo kodo za Blokiraj RAM ter ustrezno uredite kodo in uporabite iste specifikacije širine naslovnega vodila. Ista tehnika za Altera FPGA.

Priporočena:

2019 FRC Pisanje preprostega pogonskega sklopa (Java): 5 korakov

2019 FRC Pisanje preprostega pogonskega sklopa (Java): TO NAVODILO JE ZDRAVLJENO! Prosim, bodite pozorni na moj naslednji pouk o trenutnem programiranju za leto 2019. Čeprav je zastarela, se o njej lahko naučite še nekaj, na primer, kako dejansko narediti razrede in napisati kodo

Zasnova programabilnega krmilnika prekinitev v VHDL: 4 koraki

Oblikovanje programabilnega krmilnika prekinitev v VHDL: Presenečen sem nad vrstami odzivov, ki jih dobim v tem blogu. Hvala, fantje, ki ste obiskali moj blog in me spodbudili, da svoje znanje delim z vami. Tokrat bom predstavil zasnovo drugega zanimivega modula, ki ga vidimo v vseh SOC -jih - Interrupt C

Zasnova enostavnega krmilnika predpomnilnika v VHDL: 4 koraki

Oblikovanje enostavnega krmilnika predpomnilnika v VHDL: Pišem to navodilo, ker se mi je zdelo malo težko pridobiti referenčno kodo VHDL, da bi se naučili in začeli oblikovati krmilnik predpomnilnika. Zato sem sam iz nič oblikoval krmilnik predpomnilnika in ga uspešno preizkusil na FPGA. Imam p

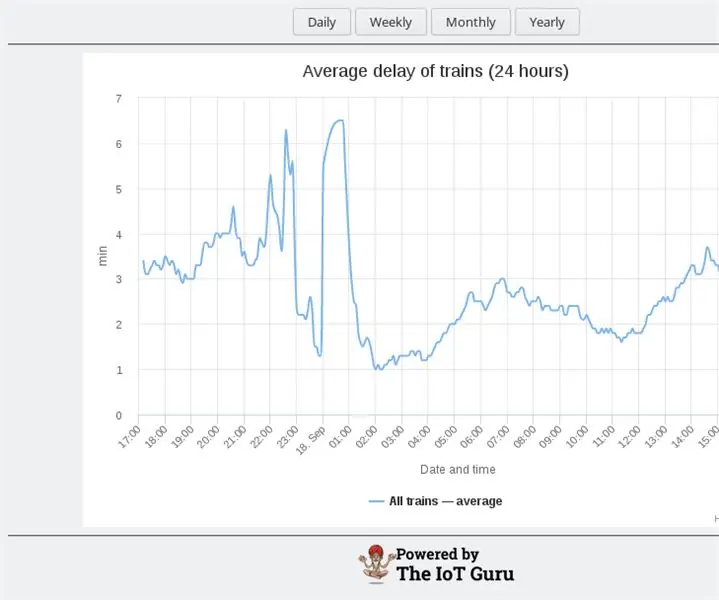

IoT Guru Cloud - Primer preprostega grafikona: 4 koraki

IoT Guru Cloud - Enostavni primer grafikona: IoT Guru Cloud ponuja kup zalednih storitev prek API -ja REST in te klice REST lahko preprosto vključite v svojo spletno stran. Z Highcharts lahko preprosto prikažete grafikone svojih meritev s klicem AJAX

Zasnova enostavnega krmilnika VGA v VHDL in Verilogu: 5 korakov

Oblikovanje preprostega krmilnika VGA v VHDL in Verilogu: V tem navodilu bomo zasnovali preprost krmilnik VGA v RTL. VGA krmilnik je digitalno vezje, zasnovano za pogon zaslonov VGA. Bere iz pomnilnika okvirja (pomnilnik VGA), ki predstavlja okvir za prikaz, in ustvari naslednje