Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:05.

- Nazadnje spremenjeno 2025-01-23 15:09.

Cilj tega projekta je ustvariti funkcionalnost prikaza slike pametnega ogledala. Zrcalo lahko prikaže napovedi (sončno, delno sončno, oblačno, vetrovno, dež, grmenje in sneg) in vrednosti temperature od -9999 ° do 9999 °. Napovedne in temperaturne vrednosti so težko kodirane, kot da bi posnemale njihovo razčlenitev iz vremenskega API -ja.

Projekt uporablja ploščo Zynq-Zybo-7000 s sistemom FreeRTOS in uporablja Vivado 2018.2 za oblikovanje in programiranje strojne opreme.

Deli:

Zynq-Zybo-7000 (z FreeRTOS)

19 -palčni LCD (640x480)

VGA kabel

12 "x 18" ogledalo iz akrila

1. korak: Konfiguriranje Vivada

Prenesite Vivado 2018.2 iz Xilinxa in uporabite licenco Webpack. Zaženite Vivado in "Ustvari nov projekt" in mu dajte ime. Nato izberite "RTL Project" in potrdite "Trenutno ne navajajte virov." Pri izbiri dela izberite "xc7z010clg400-1" in na naslednji strani pritisnite "Dokončaj".

Korak: Pakiranje IP gonilnika VGA

Dodajte datoteko vga_driver.sv v vire oblikovanja. Nato kliknite »Orodja« in izberite »Ustvari in zapakiraj nov IP«. Izberite "Pakiraj svoj trenutni projekt." Nato izberite lokacijo IP in "Vključi datoteke.xci." V pojavnem oknu kliknite »V redu« in nato »Dokončaj«.

V razdelku »Koraki pakiranja« pojdite na »Pregled in paket« in izberite »Paket IP«.

Zdaj bi moral biti vga_driver na voljo kot blok IP.

Korak: Zynq IP

V razdelku "IP Integrator" izberite "Create Block Design". Dodajte "ZYNQ7 Processing System" in dvokliknite blok. Kliknite "Uvozi nastavitve XPS" in naložite datoteko ZYBO_zynq_def.xml.

Nato pod "Konfiguracija PS-PL" odprite spustni meni za "AXI Non Secure Enablement" in preverite "M AXI GP0 interface".

Nato pod "MIO Configuration" odprite spustni meni za "Application Processor Unit" in preverite "Timer 0" in "Watchdog".

Nazadnje, pod "Clock Configuration" odprite spustni meni za "PL Fabric Clocks" in preverite "FCLK_CLK0" in na 100 MHz.

4. korak: GPIO IP

Oblikovanju blokov dodajte dva bloka GPIO. GPIO -ji bodo uporabljeni za nadzor naslova slikovnih pik in komponent RGB slikovnih pik. Konfigurirajte bloke, kot je prikazano na zgornjih slikah. Ko dodate in konfigurirate oba bloka, kliknite »Zaženi samodejno povezovanje«.

GPIO 0 - 1. kanal nadzoruje naslov slikovne pike, 2. kanal pa rdečo barvo.

GPIO 1 - Kanal 1 nadzoruje zeleno barvo, kanal 2 pa modro barvo.

5. korak: Blokirajte pomnilnik

IP -ju generatorja pomnilnika blokov dodajte oblikovanje blokov in konfigurirajte, kot je prikazano zgoraj. Barve slikovnih pik so zapisane na pomnilniške naslove, ki jih nato prebere gonilnik VGA. Naslovna vrstica mora ustrezati količini pikslov, ki se uporabljajo, zato mora biti 16 bitov. Podatki so prav tako 16 bitov, saj je 16 barvnih bitov. Ne zanima nas branje potrditvenih kosov.

6. korak: Drugi IP

V priloženem pdf -ju je prikazana dokončana zasnova bloka. Dodajte manjkajoči IP in dokončajte povezave. Prav tako "Make Externals" za barvne izhode VGA ter navpične in vodoravne izhode za sinhronizacijo.

xlconcat_0 - poveže posamezne barve, da tvori en 16 -bitni signal RGB, ki se vnese v blok RAM.

xlconcat_1 - poveže signale stolpcev in vrstic iz gonilnika VGA in se vnese v vrata B blokovskega RAM -a. To gonilniku VGA omogoča branje barvnih vrednosti slikovnih pik.

VDD - konstanta HIGH, povezana z možnostjo pisanja blokovskega RAM -a, tako da imamo vedno pravico do tega.

xlslice_0, 1, 2 - Rezine se uporabljajo za razbijanje signala RGB v posamezne signale R, G in B, ki jih je mogoče vnesti v gonilnik VGA.

Ko je zasnova bloka končana, ustvarite ovoj HDL in dodajte datoteko omejitev.

*Block Design temelji na vadnici, ki jo je napisal benlin1994*

7. korak: SDK

Koda, ki izvaja to oblikovanje blokov, je vključena spodaj. Init.c vsebuje funkcije, ki upravljajo risbo (napovedi, številke, simbol stopinje itd.). Glavna zanka v main.c je tisto, kar se izvaja, ko je plošča programirana. Ta zanka nastavi napoved in temperaturo ter nato pokliče funkcije risanja v init.c. Trenutno pregleduje vseh sedem napovedi in se prikazuje eno za drugo. Priporočljivo je, da v vrstico 239 dodate prelomno točko, da si lahko ogledate vsako sliko. Koda je komentirana in vam bo dala več informacij.

8. korak: Zaključek

Za izboljšanje trenutnega projekta bi lahko naložili prednaložene slike napovedi v obliki datotek COE v Block Memory Generators. Namesto da bi ročno črpali napovedi, kot smo to počeli v kodi C, bi lahko prebrali slike. Poskušali smo to narediti, vendar ni uspelo. Vrednosti slikovnih pik smo lahko prebrali in jih prikazali, vendar je ustvarila neurejene slike, ki niso bile podobne tistim, ki smo jih naložili v RAM. Podatkovni list Block Memory Generator je uporaben za branje.

Projekt je v bistvu pol pametnega ogledala, saj mu manjka vidik internetne povezljivosti. Če bi to dodali, bi dobili popolno pametno ogledalo.

Priporočena:

TTGO (barvni) zaslon z mikropythonom (T-zaslon TTGO): 6 korakov

TTGO (barvni) zaslon z Micropythonom (TTGO T-zaslon): TTGO T-zaslon je plošča, ki temelji na ESP32 in vključuje 1,14-palčni barvni zaslon. Ploščo lahko kupite za nagrado manj kot 7 $ (vključno z ladijskim prometom, nagrado na banggoodu). To je neverjetna nagrada za ESP32, vključno z zaslonom

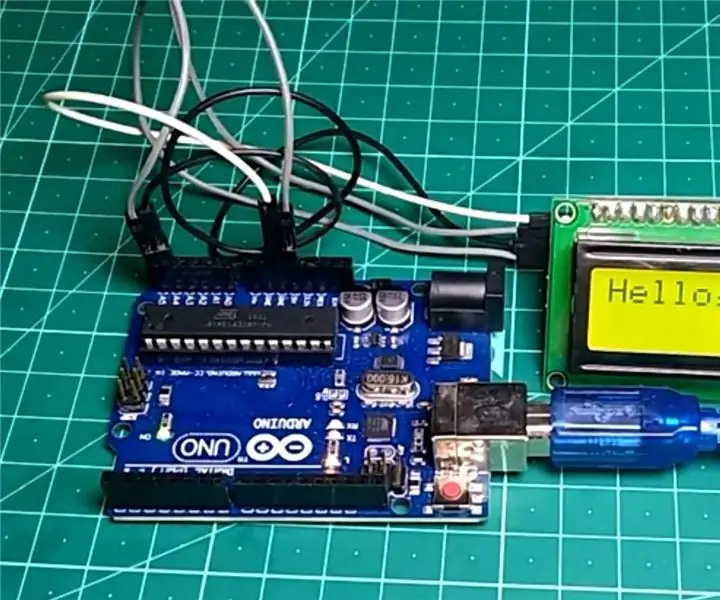

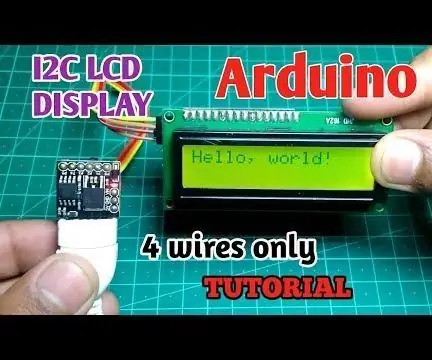

I2C / IIC LCD zaslon - Uporabite SPI LCD za LCD zaslon I2C z uporabo modula SPI do IIC z Arduinom: 5 korakov

I2C / IIC LCD zaslon | Uporabite SPI LCD za LCD zaslon I2C z uporabo modula SPI do IIC z Arduinom: Pozdravljeni, saj ima navaden SPI LCD 1602 preveč žic za povezavo, zato ga je zelo težko povezati z arduinom, vendar je na trgu na voljo en modul, ki lahko pretvorite zaslon SPI v zaslon IIC, tako da morate priključiti samo 4 žice

I2C / IIC LCD zaslon - Pretvorite SPI LCD v LCD zaslon I2C: 5 korakov

I2C / IIC LCD zaslon | Pretvorite SPI LCD v LCD zaslon I2C: uporaba spi lcd zaslona zahteva preveč povezav, kar je res težko narediti, zato sem našel modul, ki lahko i2c lcd pretvori v spi lcd, zato začnimo

Zrcalni brisalnik: 4 koraki

Brisalec ogledal: Veliko ljudi moti megla v kopalniškem ogledalu doma. Vsakič, ko se stuširajo, je na ogledalu debela plast megle. Ko ga obrišete s krpo, se bo spet zameglilo in ne bo prišlo do ogledala. V primeru dežja

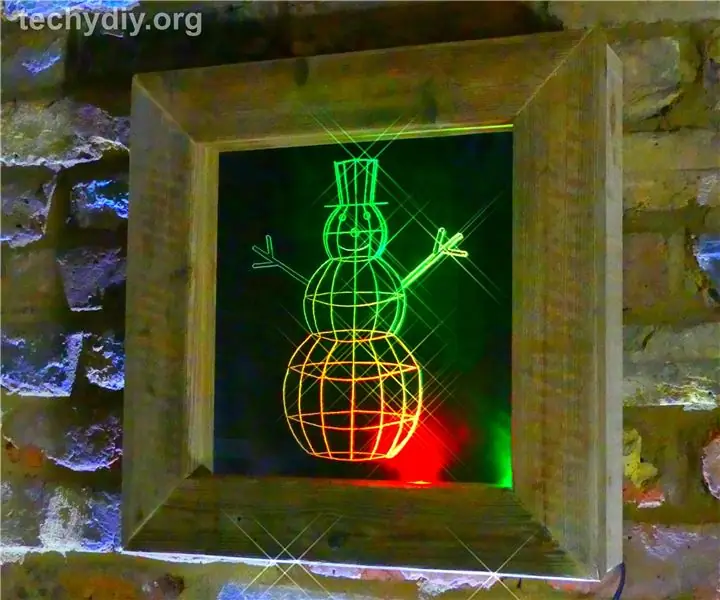

Zrcalni znak prižganega snežaka Led Edge: 21 korakov (s slikami)

Zrcalni znak Snežak z osvetljenim robom: V tem navodilu bom opisal, kako lahko naredite stekleno ogledalo z osvetljenim robom s snežakom, ki je kot nalašč za božič! Znak je vklesan na stekleno ogledalo iz Ikee. Ti so v štirih pakiranjih in so precej stroškovno učinkoviti. JAZ