Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:08.

- Nazadnje spremenjeno 2025-01-23 15:09.

To je vadnica o tem, kako sestaviti enominutno štoparico z uporabo VHDL in plošče Basys 3. Takšna naprava je idealna za igre, kjer ima vsak igralec na voljo največ eno minuto. Štoparica natančno prikaže sekunde in milisekunde na zaslonu sedmih segmentov, začenši od 0 sekund in 0 milisekund, do 60 sekund in 0 milisekund. Uporabljata se tudi dva gumba: osrednji gumb, ki se uporablja za zagon, ustavitev in nadaljevanje časovnika, ter desni gumb, ki se uporablja za ponovni zagon časovnika. Ko napravo primerjamo vzporedno z vgrajeno štoparico pametnega telefona, je natančnost ure opazna.

1. korak: Pridobite strojno/programsko opremo

1. Basys 3 Artix-7 FPGA Trainer Board od Digilenta s kablom Micro-USB do USB

2. Vivado 2016.2 Design Suite iz Xilinxa

2. korak: blokovni diagram

To vezje je zgrajeno vedenjsko in uporablja vgrajene komponente Xilinx, lahko pa ga opišemo tudi strukturno, kot kaže zgornji splošni strukturni diagram. Iz diagrama je razvidno, da vezje poganjata dva frekvenčna delilnika. Eden od frekvenčnih delilnikov deluje pri 1 centisekundi in poganja katodni števec, ki se uporablja kot številke, prikazane na sedem-segmentnem zaslonu. Drugi frekvenčni delilnik deluje pri 240Hz in se uporablja za pogon anodnega števca, ki se vrti skozi anode, tako da se vse številke pravilno prikažejo na sedem-segmentnem zaslonu. Dajalnik vzame katodno logiko iz katodnega števca in anodno logiko iz anodnega števca ter jo kodira na izhodno katodo in anodo, ki poganja sedem-segmentni zaslon. Funkcija tega dajalnika je, da se katodni izhod spremeni vsakič, ko se anodni izhod spremeni. Izhoda katode ni mogoče izvajati neodvisno od števca, ker se morajo anode vrteti skozi 4 ločene številke.

3. korak: Modul projekta

Najprej se naredi procesni blok za CEN, tako da se ob zaznavi pritiska na gumb ENABLE preklopi. To služi kot zaustavitev/zagon katodnega števca.

V naslednjem procesnem bloku sta centisekundni in 240Hz taktni signal nastavljena tako, da se njihovi števci povečajo za 1 vsakič, ko notranja ura 100mHz doseže naraščajoč rob. Ko števec centisekunde doseže 500000, bi se ponastavil nazaj na 0. Medtem bi se števec 240Hz ponastavil, ko štetje doseže 41667.

Za del katode kode, če je ENABLE '0', se bo štetje katod ustavilo. Če v tem času pritisnete gumb za ponastavitev, se vsa števila ponastavijo na "0000". Če je ENABLE "1", se bo štetje katod nadaljevalo, dokler število katod ne doseže 60,00, pri čemer sproži signal za zaustavitev na "1". Signal za zaustavitev se vrne nazaj v procesni blok CEN in povzroči možnost ENABLE '0', medtem ko je signal za zaustavitev '1' in se ne spremeni, dokler ne pritisnete gumba za ponastavitev.

Nazadnje je sedem segmentni zaslon nastavljen tako, da so 4 anode pravilno povezane z vsako od svojih 8 katod, da hkrati prikažejo svoje števke 0-9.

4. korak: Omejitve

Ta datoteka omejitev povezuje določene vhode in izhode iz VHDL v potrebne fizične dele plošče Basys. Za ta projekt komponente vključujejo štiri anode in vsako od njihovih osmih katod za sedem segmentni zaslon, notranjo uro 100 mHz, sredinski gumb in desni gumb.

5. korak: Preizkusite

Ko dokončate kodo, lahko zdaj programirate FPGA prek kabla USB. Prikaz sedmih segmentov mora prikazati 0,00. Preverite, ali gumbi delujejo, tako da pritisnete osrednji gumb za zagon časovnika, dokler ne doseže 60,00 in se ustavi; kadar koli vmes, lahko znova pritisnete osrednji gumb, da ga začasno ustavite. Ko je začasno ustavljen, lahko pritisnete desni gumb, da časovnik ponastavite nazaj na 0,00. Če vse deluje pravilno, čestitam, pravkar ste zgradili enominutni časomer!

Priporočena:

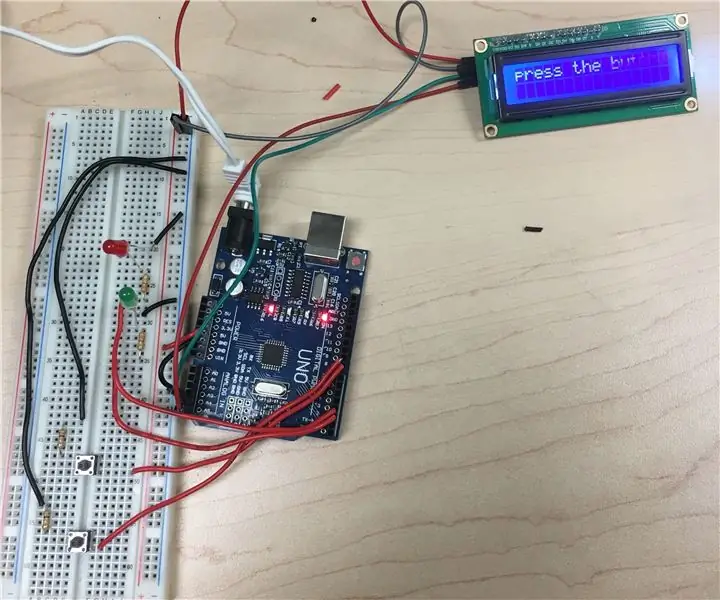

Štoparica Arduino z uporabo I2C LCD: 5 korakov

Štoparica Arduino z uporabo I2C LCD: V tem projektu vas bom naučil uporabljati LCD zaslon in Arduino kot interaktivno štoparico. Ko je vaš projekt končan s kodo, bi morala izgledati kot zgornja fotografija. Pojdite na naslednji korak, če želite izvedeti, kje začeti

Samodejna štoparica: 9 korakov

Samodejna štoparica: Ta navodila vam bodo pokazala, kako sestaviti avtomatsko štoparico. Ker je tek zabaven, včasih pa ob sebi nimaš nikogar, ki bi te imel čas. Poskušal sem biti čim bolj preprost, poceni in natančen. Ne potrebujete daljinskega upravljalnika

Štoparica brez programiranja: 5 korakov

Štoparica brez programiranja: Hej fantje, za vse začetnike je tukaj kul projekt, ki ga lahko ustvarite brez programiranja. Je preprost in tudi stroškovno učinkovit. Preden začnemo, si oglejmo seznam delov: uporabljeni IC: 1) merilnik časa 555- x12) CD 4081BE (IN g

Osnovna štoparica z uporabo VHDL in plošče Basys3: 9 korakov

Osnovna štoparica z uporabo plošče VHDL in Basys3: Dobrodošli v navodilih za izdelavo štoparice z uporabo osnovnih plošč VHDL in Basys 3. Z veseljem delimo naš projekt z vami! To je bil zadnji projekt za tečaj CPE 133 (digitalno oblikovanje) na Cal Poly, SLO jeseni 2016. Projekt, ki smo ga zgradili

Štoparica VHDL: 8 korakov (s slikami)

Štoparica VHDL: To je vadnica o tem, kako narediti štoparico z uporabo VHDL in vezja FPGA, kot je plošča Basys3 Atrix-7. Štoparica lahko šteje od 00,00 sekund do 99,99 sekund. Uporablja dva gumba, enega za gumb za zagon/ustavitev in drugega za tipko