Kazalo:

- 1. korak: blokovni diagram

- 2. korak: Načelo delovanja

- 3. korak: Izvajanje logike

- 4. korak: Odprava zastoja

- 5. korak: Konfiguracija naprave - vezje Matrix0

- 6. korak: Konfiguracija naprave - logika ure SPI

- 7. korak: Konfiguracija naprave - Lastnosti komponent Matrix0

- 8. korak: Konfiguracija naprave - vezje Matrix1

- 9. korak: Konfiguracija naprave - 3 -bitni binarni števec

- 10. korak: Konfiguracija naprave - 3 -bitna logika za primerjavo

- 11. korak: Konfiguracija naprave - Logika digitalnega primerjanja in začasni register

- 12. korak: Konfiguracija naprave - Lastnosti komponent Matrix1

- 13. korak: Rezultati

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:03.

- Nazadnje spremenjeno 2025-01-23 15:08.

Krmilni sistemi in z njimi povezane naprave se ukvarjajo z več viri energije, kot so prednapetostne linije ali baterije, in morajo slediti najvišji (ali najnižji) liniji v danem nizu.

Na primer, preklapljanje obremenitve v sistemu z več baterijami zahteva, da sistem nadzira najmanjšo ali največjo napetost med nizom baterij (max ali min kot funkcija določenega preklopnega algoritma) in dinamično usmerja breme na najprimernejši vir v realnem času. Druga možnost je, da bo sistem za pravilno polnjenje morda začasno odklopil baterijo z najnižjo napetostjo.

Drug primer je sodoben sistem sončne energije, kjer je vsaka sončna plošča opremljena z nagibnim mehanizmom in s solarnim krogom za sledenje (slednji zagotavlja informacije o položaju Sonca za orientacijo plošče). Z informacijami o največji napetosti je mogoče vsak položaj solarne plošče natančno prilagoditi na podlagi, da plošča niza dejansko prinaša najvišjo izhodno napetost, s čimer se doseže vrhunska raven optimizacije moči.

Obstaja več različnih blagovnih znamk komercialnih IC (predvsem mikrokrmilnikov), ki načeloma lahko izvajajo sledilnik največje napetosti. Zahtevajo programiranje in so manj stroškovno učinkoviti kot rešitev z mešanim signalom. Dopolnitev zasnove Dialog GreenPAKTM lahko pozitivno vpliva na cenovno dostopnost, velikost in modularnost zasnove. Ta zasnova izkorišča prednosti integracije analognega in digitalnega vezja v en sam čip.

V tem Instructableu je vgrajen analogni sprednji del in digitalna logika, ki je potrebna za izvajanje iskalnika največje (ali nazadnje najmanjše) napetosti med osmimi različnimi viri.

Za izvajanje 8-kanalnega analognega monitorja maks/min napetosti se uporablja SLG46620G.

Spodaj smo opisali korake, potrebne za razumevanje, kako je bila rešitev programirana za ustvarjanje 8-kanalnega analognega monitorja maksimalne/min napetosti. Če pa želite samo doseči rezultat programiranja, prenesite programsko opremo GreenPAK, če si želite ogledati že dokončano oblikovalsko datoteko GreenPAK. Priključite razvojni komplet GreenPAK na računalnik in pritisnite program, da ustvarite 8-kanalni analogni monitor maks/min napetosti.

1. korak: blokovni diagram

Slika 1 prikazuje globalni diagram izvedenega sistema.

Niz do 8 spremenljivih napetostnih virov je multipleksiran in povezan z ADP modulom GreenPAK -a, povezanim s prilagojeno notranjo zasnovo, ki lahko izbere vir z najvišjo napetostjo glede na ostale. Notranja logika te informacije odda za prikaz ali nadaljnjo obdelavo.

Zasnova temelji na izdelku GreenPAK SLG46620G, ker vključuje vse potrebne analogne in digitalne gradnike za uporabo. V tej izvedbi se matrika skenira s pomočjo analognega multiplekserja ADG508, ki ga neposredno poganja IC GreenPAK.

Izhodna informacija je 3-bitno digitalno število, ki ustreza številki vira napetosti pri največji napetosti. Neposreden način za pridobivanje teh podatkov je prikazati številko na 7-segmentnem zaslonu. To je mogoče enostavno doseči tako, da digitalni izhod SLG46620G povežete s 7-segmentnim gonilnikom zaslona, kot je rešitev GreenPAK, opisana v referenci, ali s skupno IC-jem 74LS47.

Predstavljeno vezje išče največjo napetost. Za pretvorbo zasnove v iskalnik najmanjše napetosti je treba med analognim multiplekserjem in analognim vhodom GreenPAK dodati preprosto vezje za predkondicioniranje, ki odšteje izhod multiplekserja od referenčne napetosti 1 V.

2. korak: Načelo delovanja

Zasnova ima za cilj izbrati vir z največjo napetostjo, zato se skenira celotno polje, medtem ko se shrani vrednost zadnjega maks. In se primerja z naslednjo vrednostjo na vhodu (ki pripada naslednjemu viru napetosti v skeniranju).

V nadaljevanju se bomo nanašali na celotno zaporedje multipleksiranja vzdolž vseh vhodov kot "skeniranje" ali "zanko".

Primerjava med dvema vrednostma ni dosežena s komponentami ACMP (na voljo v SLG46620G), temveč z modulom DCMP, potem ko so vrednosti digitalizirane. To je napredna in izpopolnjena tehnika, ki je bila najprej obravnavana v referenci.

Slika 2 prikazuje, kako je SLG46620G strukturiran za to zasnovo.

Analogni vhodni signal gre na ADC vhod skozi komponento PGA z nastavljenim ojačanjem 1. Z različnimi nastavitvami ojačanja lahko najdete tudi najboljše ujemanje s sprednjo elektroniko za kondicioniranje, namenjeno preslikavi vhodnih napetosti na 0-1 V obseg modula ADP GreenPAK.

ADC deluje v enosmernem načinu in pretvori analogni signal v 8-bitno digitalno kodo, ki se nato prenese v modul DCMP. Digitalna koda se vnese tudi v blok SPI, konfiguriran kot vmesnik ADC/FSM, kjer se lahko shrani digitalna koda in se ne spremeni, dokler naslednji vhod ne pride na vhod SPI CLK. Upoštevajte, da namenski logični blok poganja vhod SPI CLK. Ta del bomo raziskali kasneje, saj je to "jedrna" logika, odgovorna za pravilno delovanje. Nova digitalna koda se shrani v modul SPI le, če ustreza dejanski največji vhodni napetosti.

Komponenta DCMP se uporablja za primerjavo trenutnih podatkov ADC z zadnjim zmagovalcem (to je zadnji največji najdeni), ki je shranjen v bloku SPI. Na izhodu OUT+ bo ustvaril impulz, ko bodo novi podatki ADC večji od prejšnjih. Signal OUT+ uporabljamo za posodobitev bloka SPI z novim zmagovalcem.

Globalni signal ure poganja pretvorbe ADC in splošne časovne razporede. Ko je pretvorba izvedena, impulzni izhodni signal ADC -ja INT utripa, časovno usklajen z vzporednim izhodom podatkov ADC. Izhod INT uporabljamo tudi za povečanje 3-bitnega binarnega števca, ki ga DFF izvajajo v Matrix1, kar je koristno iz treh razlogov:

1. Izhodne črte števca naslavljajo zunanji analogni multiplekser in tako napajajo naslednjo vhodno napetost ADC;

2. Štetje je zamrznjeno v 3-bitni register (implementirano v Matrix1) za shranjevanje začasnega zmagovalca med skeniranjem;

3. Štetje se dekodira za posodobitev drugega 3-bitnega registra (implementiranega v Matrix0), ko je skeniranje končano.

3. korak: Izvajanje logike

Modul ADC zaporedno zagotavlja pretvorjene podatke vseh vhodnih napetosti, enega za drugim, za nedoločen čas. Ko je multiplekser naslovljen na 0b111 (decimalno število 7), se števec odkotali na 0b000 (decimalni 0) in tako začne novo skeniranje vhodnih napetosti.

Med skeniranjem se izhodni signal ADC INT generira, ko je vzporedni izhod podatkov veljaven. Ko ta signal utripa, mora analogni multiplekser preklopiti na naslednji vhod, ki PGA oskrbuje z ustrezno napetostjo. Zato je izhod ADC INT neposreden taktni signal 3-bitnega binarnega števca na sliki 2, katerega 3-bitna vzporedna izhodna beseda neposredno naslavlja zunanji analogni multiplekser ("V select" na sliki 1).

Oglejmo si zdaj primer, kjer naj bi bile vhodne napetosti v naslednjih razmerjih:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Slika 3 predstavlja glavne signale, ki so vključeni v mehanizem največje odločitve.

Ker se podatki s časom sinhrono z impulzi INT shranijo v vmesni register SPI, obstaja primerjalno okno, kjer se vsebina vmesnega pomnilnika SPI primerja z naslednjim rezultatom pretvorbe ADC. Zaradi tega posebnega časa nastanejo impulzi OUT+ na izhodu DCMP. Te impulze lahko izkoristimo za nalaganje novih vrednosti v vmesni register SPI.

Kot je razvidno iz podatkovne vrstice vmesnega pomnilnika SPI prejšnje slike, register SPI od časa do časa vedno vsebuje največjo vrednost med 8 vhodi in se posodobi le, ko modul DCMP zazna večjo vrednost (nanaša se na DCMP OUT+ izhodna linija grafikona, manjkajoči impulzi povzročijo, da V2 ostane zaklenjen v registru, dokler ni v primerjavi z V5).

4. korak: Odprava zastoja

Če bi bila izvedena logika tako, kot je opisano zgoraj, je jasno, da bi naleteli na zastoj: sistem lahko zazna le napetosti, višje od tiste, ki ustreza tistemu, kar je shranjeno v vmesnem registru SPI.

To velja tudi v primeru, da bi se ta napetost zmanjšala, nato pa bi drugi vhod, doslej nižji od tega, postal najvišji: nikoli ne bi bil zaznan. To stanje je bolje razložiti na sliki 4, kjer so zaradi 3 prisotne le 3 vhodne napetosti. jasnost.

V času ponovitve 2 V3 pade in V1 je dejanska največja napetost. Toda modul DCMP ne daje impulza, ker so podatki, shranjeni v vmesnem registru SPI (kar ustreza 0,6 V), večji od podatkov, ki ustrezajo V1 (0,4 V).

Sistem se nato obnaša kot "absolutni" iskalnik največjih vrednosti in ne posodobi pravilno izhoda.

Lep način za premagovanje te težave je prisilno ponovno nalaganje podatkov v register vmesnih pomnilnikov SPI, ko sistem zaključi celoten cikel glasovanja za vse kanale.

Pravzaprav, če je napetost na tem vhodu še vedno najvišja, se nič ne spremeni in krmiljenje se varno nadaljuje (glej sliko 4 zgoraj, to velja za zanke 0 in 1). Po drugi strani pa, če se napetost na tem vhodu po naključju zniža na vrednost, manjšo od drugega vhoda, potem ponovno nalaganje vrednosti daje modulu DCMP možnost, da pri primerjavi z novo največjo vrednostjo proizvede impulz OUT+ (to je primer zanke 2 in 3).

Za premagovanje težave je potreben del logičnega vezja. Ko zanka doseže dejanski največji vhod, mora generirati taktni signal komponente SPI in tako prisiliti ponovno nalaganje svoje posodobljene podatkovne besede v vmesni register SPI. To bo obravnavano v oddelkih 7.2 in 7.6 spodaj.

5. korak: Konfiguracija naprave - vezje Matrix0

SLG46620G ima dva matrična bloka, kot je prikazano na sliki 2. Naslednje slike prikazujejo ustrezne konfiguracije naprav.

Zgornji del vezja je "Register zanke", realiziran s tremi DFF -ji (DFF0, DFF1 in DFF2). Po vsaki zanki vhodnega multiplekserja se osveži in pošlje 7-segmentnemu gonilniku zaslona binarno številko "zmagovalca", to je vhod z najvišjo napetostjo v zadnjem skeniranju. Tako ura DFF -jev kot podatki izhajajo iz logike, izvedene v Matrix1 skozi vrata P12, P13, P14 in P15.

Spodnji del je analogni sprednji del z vhodom na Pin 8 in PGA z ojačitvijo x1. Izhod ADC INT gre tako v logiko urejanja SPI kot v Matrix1 prek vrat P0, kjer bo služil kot signal ure za implementiran števec.

Vzporedna podatkovna izhoda ADC in SPI sta označena z NET11 in NET15 za povezavo s komponento DCMP v Matrix1.

6. korak: Konfiguracija naprave - logika ure SPI

Kot je bilo že omenjeno v razdelku »Izvajanje logike«, se register vmesnega pomnilnika SPI posodobi vsakič, ko primerjava med dejansko shranjeno vrednostjo in novimi podatki o pretvorbi ADC ustvari impulz na izhodu DCMP OUT+.

Celovitost signala je zagotovljena, če je ta signal AND-ed z izhodom ADC INT. S tem se izognete kakršnim koli skokom in lažnim sprožanjem.

Poudarili smo tudi, da je za preskok zastojev treba vmesni pomnilnik SPI posodobiti, ko zanka doseže podatke o dejanskem zmagovalcu.

Za pravilno delovanje SPI so v igri trije signali:

1. Izhod ADC INT (LUT0-IN1)

2. DCMP OUT+ izhod (LUT0-IN0 prek vrat P10)

3. Štetje je enako signalu zapaha (LUT0-IN2 prek vrat P11)

Prva dva sta AND-ed in oba OR-ed s slednjim v LUT0, katerega izvedba je konfigurirana kot na sliki 6.

7. korak: Konfiguracija naprave - Lastnosti komponent Matrix0

Slike 7-10 prikazujejo preostala okna lastnosti komponent, ki pripadajo Matrix0.

8. korak: Konfiguracija naprave - vezje Matrix1

9. korak: Konfiguracija naprave - 3 -bitni binarni števec

Zgornji del vezja vsebuje logične elemente, predvsem 3-bitni binarni števec, ki deluje na izhodu ADC INT, kot je že bilo opisano. Ta števec je izveden s precej "standardno" shemo, prikazano na sliki 12.

Ta števec je v naši zasnovi realiziran s pomočjo natikačev DFF9, DFF10, DFF11 in INV1, LUT4, LUT8. Izhod DFF9 je LSB, DFF11 pa MSB, kot je prikazano na sliki 13.

LUT4 je konfiguriran kot XOR, medtem ko LUT8 izvaja logiko AND-XOR na sliki 12.

Številčni izhodi gredo na tri digitalne izhodne zatiče za obravnavo zunanjega analognega multiplekserja.

LUT10 dekodira kodo števca, ko je skeniranje končano, in posreduje impulz v Matrix0 prek DLY8 in vrat P12. To preprosto dosežemo z AND-ing izhodi števca in s tem dekodiramo številko 7 dec (0b111 binarno, konec zanke).

10. korak: Konfiguracija naprave - 3 -bitna logika za primerjavo

Slika 15 prikazuje vezje, ki se uporablja za zaznavanje, ko zanka ponavlja na trenutnem naslovu »zmagovalec«. V tem primeru, kot je že bilo razloženo, bi moral digitalni impulz prisiliti ponovno nalaganje trenutnega rezultata ADC, da bi rešil morebitno zastoj.

Naslov »zmagovalca« je shranjen v začasnem registru Matrix1 (glej spodaj), trenutni naslov pa izpiše binarni števec.

Vrata XNOR zagotavljajo pravilen (logični 1 ali "visok") izhod, ko sta oba vhoda enaka. In ta signal za vse bite (LUT9) nam daje utrip, ko sta obe binarni kodi enaki. Podrobnosti o vratih XOR kot preverjalcu parnosti najdete v Reference.

Signal "Counter-equals-Latch" se posreduje Matrix0 prek vrat P11.

11. korak: Konfiguracija naprave - Logika digitalnega primerjanja in začasni register

Spodnji del slike 11 (označen na sliki 16) prikazuje blok DCMP, ki je del odločanja pri tej zasnovi.

DFF6, 7 in 8 tvorijo 3-bitni register za shranjevanje začasne vhodne številke "zmagovalec", medtem ko je zanka v teku. Vhod na japonke so 3-bitni izhodi binarnih števcev, kot so vidni v globalnem vezju Matrix1 na sliki 11, ki so zaradi jasnosti tukaj preskočeni.

Izhodi tega registra ne morejo neposredno poganjati 7-segmentnega zaslona, ker se tukaj shranjena vrednost med skeniranjem spremeni in bi jo bilo treba šteti za „veljavno“šele na koncu samega skeniranja.

Zaradi tega se izhodi začasnega registra povežejo z registrom zanke Matrix0 prek med matričnih vrat P13, P14 in P15.

Na sliki 16 je pomembno opaziti, da se začasni register zaklene z izhodom DCMP OUT+, ko ADC-SPI zabeleži primerjalne rezultate pri ugotovljenem novem maks.

Isti signal OUT+ se prek vrat P10 posreduje Matrix0, SPI CLK Logic.

12. korak: Konfiguracija naprave - Lastnosti komponent Matrix1

Slike 17-19 prikazujejo okna lastnosti komponent, ki pripadajo Matrix1.

13. korak: Rezultati

Za preizkus izvedbe je bil izdelan prototip ocenjevalne plošče, kjer 8 analognih vhodnih napetosti pridobi niz upornih delilnikov s TrimPots (kot je prikazano na sliki 20).

Uporabljeni multiplekser je ADG508, del, ki lahko deluje z enim napajanjem (12 V).

7-segmentni gonilnik zaslona je 74LS47. Dekodira vzporedno vhodno besedo in neposredno upravlja 7-segmentni zaslon s skupno anodo.

Ocenjevalna plošča ima pravokotni konektor 2x10 za neposredno priključitev na napredno razvojno platformo GreenPAK na svojem razširitvenem priključku, kot je prikazano na sliki 21.

V povezavi z napredno razvojno platformo GreenPAK omogoča zelo preprosto merjenje signalov za hitro preverjanje. Na sliki 22 je na primer prikazan niz signalov (oziroma ura, izhod ADC INT in izhod DCMP OUT+), ki jih zajame logični analizator HP 54620A. Valovne oblike sproži naraščajoči rob signala OUT+ (v obsegu, označenem kot 'A> B'), zato je to zajem valovne oblike, ko se med analognimi vhodi zazna nova največja napetost. Pravzaprav je bila pridobljena z vrtenjem enega od trimpotov ocenjevalne deske, da se poveča ustrezna napetost, prikazana na sliki 22.

Slika 23 prikazuje shemo ocenjevalne komisije.

Zaključek

V tem navodilu smo uvedli osemkanalni iskalnik največje (ali najmanjše) napetosti, ki ga bomo uporabljali kot običajen dodatek k večkanalnim krmilnim sistemom. Predstavljeni pristop izkorišča napredne funkcije komponent GreenPAK in prikazuje, kako je mogoče integrirati v en sam čip analogne in digitalne funkcije. Več komercialnih IC -jev je mogoče zamenjati z Dialog GreenPAK -i, tako da se lahko zmanjšata velikost in stroški aplikacije.

Priporočena:

Merilnik enosmerne napetosti za žep velikosti DIY: 5 korakov

DIY žepni merilnik enosmerne napetosti: v tem navodilu vam bom pokazal, kako lahko sami naredite merilnik enosmerne napetosti enosmerne napetosti velikosti DIY s piezo zvočnikom za preverjanje vezja. Vse kar potrebujete je osnovno znanje o elektroniki in nekaj časa. Če imate kakršna koli vprašanja ali težave, lahko

Naredite najmanjše enojne uravnotežene ušesne čepke na svetu: 7 korakov (s slikami)

Naredite najmanjše enojne uravnotežene ušesne čepke na svetu: To je projekt, ki bo verjetno naredil najmanjše posamezne BA ušesne čepke z avdiofilno kakovostjo zvoka. Oblikovanje je navdihnilo Final F7200, IEM z visoko ločljivostjo 400 USD+ na Amazon. Medtem ko so komponente na voljo na odprtem trgu, lahko DIY -ji uspejo v

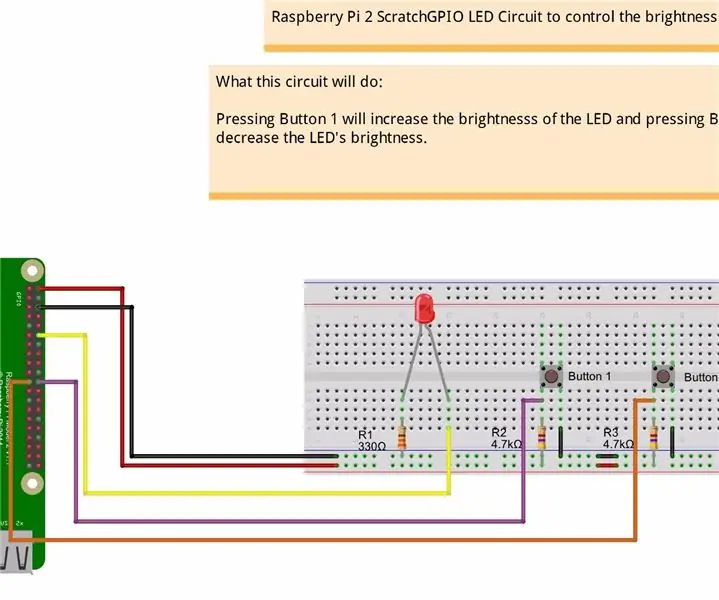

Nadzor svetlosti PWM LED nadzor s potisnimi gumbi, Raspberry Pi in Scratch: 8 korakov (s slikami)

Nadzor svetlosti Upravljanje LED na osnovi PWM s potisnimi gumbi, Raspberry Pi in Scratch: poskušal sem najti način, kako svojim učencem razložiti, kako deluje PWM, zato sem si zadal nalogo, da poskušam nadzorovati svetlost LED z dvema gumboma - en gumb poveča svetlost LED, drugi pa ga zatemni. Za program

Največje imetje: vdrl sem v star telefon, da bi predvajal glasbo z največjim zadržanjem .: 13 korakov (s slikami)

Največje imetje: vdrl sem v star telefon za predvajanje glasbe z največjo zadržanostjo .: https: //youtu.be/Ma4QnfQ7Dxo No … Prepričan sem, da ne želite telefona, ki samo predvaja glasbo z zadržanjem … Ampak s tem zelo preprostim kramom teh lahko dostopnih "pisalnih miz" lahko naredite nešteto drugih razburljivih projektov telefonov.

Hidroponski sistem za nadzor in nadzor rastlinjaka: 5 korakov (s slikami)

Hidroponski sistem za nadzor in nadzor rastlinjakov: V tem navodilu vam bom pokazal, kako sestaviti hidroponski sistem za nadzor in nadzor rastlinjakov. Pokazal vam bom izbrane komponente, diagram ožičenja, kako je bilo vezje zgrajeno, in skico Arduino, uporabljeno za programiranje Seeed