Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:03.

- Nazadnje spremenjeno 2025-01-23 15:08.

S tem ščitom povežite svojo razvojno ploščo Mojo z zunanjimi vhodi.

Kaj je razvojna plošča Mojo?

Razvojna plošča Mojo je razvojna plošča, ki temelji na Xilinx spartan 3 FPGA. Ploščo izdeluje Alchitry. FPGA so zelo uporabne, kadar je treba hkrati izvajati več procesov.

Kaj boste potrebovali?

Zaloge

Mojo razvojna plošča

Gerberjeva datoteka

8 x 15 k ohmski upori (neobvezno*)

4 x 470 ohmski upori

4 x 560 ohmski upori

4 x CC sedem segmentni zasloni

4 x 3 mm LED

4 x taktilna stikala SPDT

1 x 4 -položajno DIP stikalo za površinsko montažo

2 x 25 do 2 ali 4 x 25 glav

1x 2 x 5 -polna glava škatle

Spajkalnik

Spajkanje

Flux

*(če so ti upori izpuščeni, je treba za ustrezne zatiče omogočiti notranji dvig/spuščanje)

Korak: Naložite Gerber na proizvajalca tiskane plošče po vaši izbiri

Za svoje plošče sem naročil pri JLC PCB.

Edina sprememba, ki sem jo naredil, je bila barva, ki sem jo želela ujemati s črno Mojo.

2. korak: sestava odbora

Pri spajkanju se mi vedno zdi koristno najprej spajkati najnižje dele, zato je dobro začeti z upori.

R5, R6, R7, R8, R9, R10, R11 in R12 so 15k ohmski upori, ki se uporabljajo za spuščanje stikal (če uporabljate notranji dvig/spuščanje, tega ne upoštevajte).

R1, R2, R3, R4 so 560 ohmski upori, ki so odgovorni za omejevanje toka skozi 7 -segmentni zaslon.

R13, R14, R15, R16 so 470 ohmski upori, ki so odgovorni za omejevanje toka skozi 4 LED diode.

Nato spajkajte potopno stikalo, taktilna stikala, LED diode, sedem segmentne zaslone in priključek glave polja v tem vrstnem redu.

Zdaj postavite 25 x 2 (ali 2 25 x 1) v mojo, da poravnate zatiče. Poravnajte ščit s čepi in ga spajkajte.

3. korak: Namestitev programske opreme

Za programsko opremo, ki se nanaša na spletno mesto Alchitry, boste vedeli, kaj potrebujete za začetek in namestitev Xilinx ISE. Vendar spremenite datoteko.ucf, da bo vedela, kateri zatiči so povezani s tem, kar je pomembno za zagon vašega programa.

Tu je datoteka.ucf, ki jo uporabljam s ščitom:

KONFIGIRAJ VCCAUX = 3,3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = OBDOBJE "clk" 50 MHz VISOKO 50%; NETO "clk" LOC = P56 | IOSTANDARD = LVTTL; NETO "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NETO "cclk" LOC = P70 | IOSTANDARD = LVTTL; NETO "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NETO "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NETO "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NETO "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NETO "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NETO "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NETO "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NETO "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NETO "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NETO "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NETO "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NETO "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NETO "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NETO "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NETO "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NETO "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NETO "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NETO "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Ne pozabite, če niste namestili spustnih uporov za urejanje nožic v.ucf

| POVOLČEN; o

| DVIGNI;

Če želite blok uporabiti za karkoli, so povezave naslednje. Levo je številka pin bloka, desno pa številka mojo pin, ki jo morate dodeliti v svojem.ucf:

pin 1 = 29

pin 2 = 51

pin 3 = 32

nožica 4 = 41

pin 5 = 34

nožica 6 = 35

nožica 7 = 40

nožica 8 = 33

nožica 9 = GND

nožica 10 = +V

Priporočena:

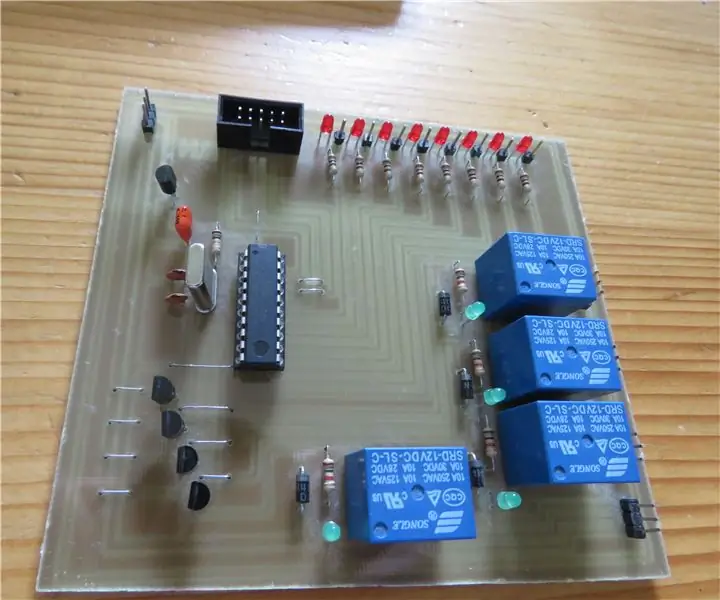

Naredite svojo razvojno ploščo z mikrokrmilnikom: 3 koraki (s slikami)

Naredite svojo razvojno ploščo z mikrokrmilnikom: Ali ste kdaj želeli izdelati svojo razvojno ploščo z mikrokrmilnikom, pa niste vedeli, kako? V tem navodilu vam bom pokazal, kako to narediti. Vse, kar potrebujete, je znanje o elektroniki, oblikovanje vezij in programiranje. Če imate kakšno iskanje

Igranje igre Flappy Bird z razvojno ploščo M5stack Esp32 na osnovi M5stick C: 5 korakov

Igranje igre Flappy Bird z razvojno ploščo M5stack Esp32 na osnovi M5stick C: Pozdravljeni, danes se bomo naučili, kako naložiti kodo igre flappy bird na razvojno ploščo m5stick c, ki jo ponuja m5stack. Za ta majhen projekt boste potrebovali dve stvari: m5stick-c razvojna plošča: https://www.utsource.net/itm/p/8663561.h

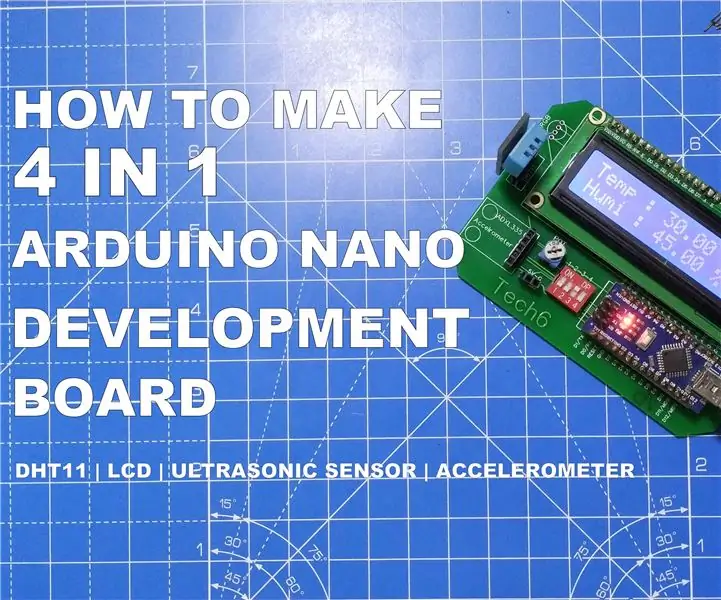

Kako narediti Arduino Nano razvojno ploščo 4 v 1: 4 koraki

Kako narediti razvojno ploščo Arduino Nano 4 v 1: V tem navodilu se boste naučili, kako narediti razvojno ploščo Arduino Nano. Razvojna plošča Arduino nano ima vgrajene reže za ultrazvočni senzor (HCSR-04), merilnik pospeška, senzor DHT11 in zaslon s tekočimi kristali (LCD). Ta bo

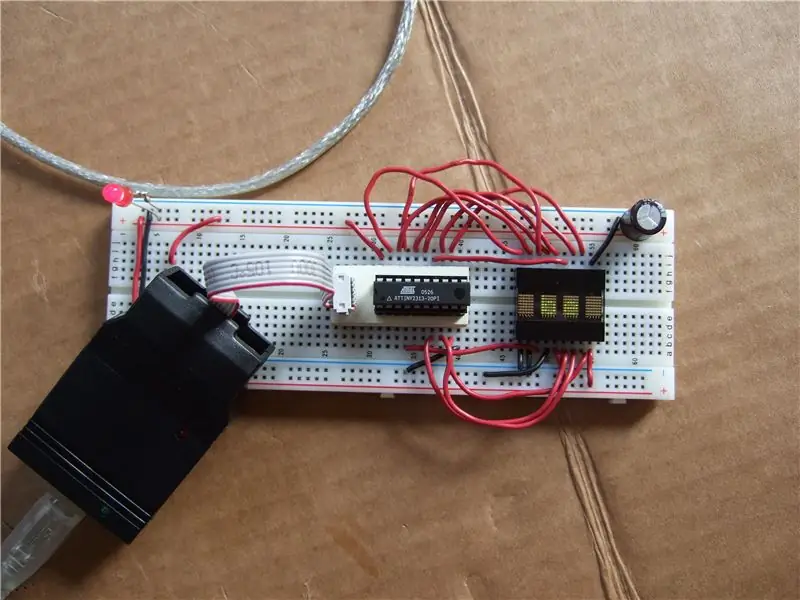

Razvojno okolje geta: 5 korakov

Razvojno okolje geta: Pred časom sem objavil hiter in umazan " el cheapo " način, kako začeti s programiranjem čipov serije Atmel AVR: Ghetto Programmer (različica 1.0) Od takrat sem vampiral, ponovno vampiral in drugače izboljšal nastavitve. Mislil sem, da bo

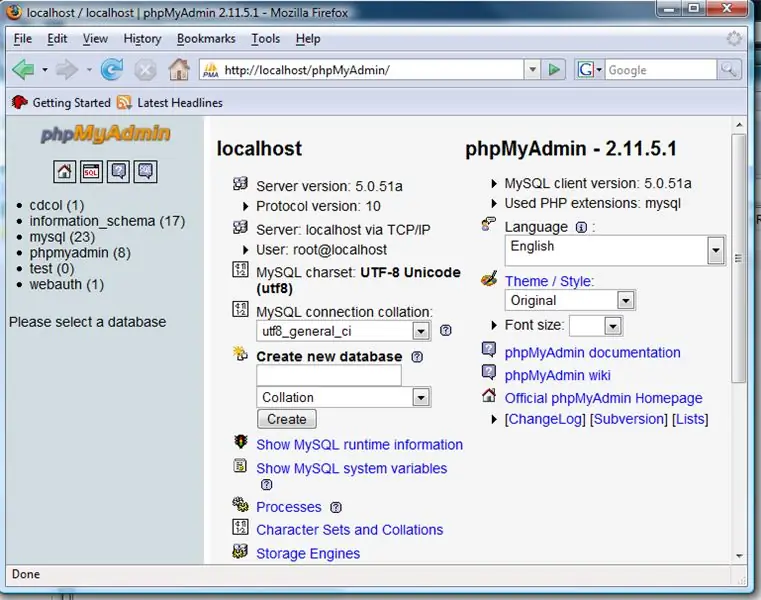

Kako namestiti spletno razvojno okolje na Localhost: 6 korakov

Kako namestiti spletno razvojno okolje na Localhost: Ta navodila vam bodo pokazala, kako namestiti Apache, PHP, MySQL na localhost. Prav tako, kako ga nastaviti tako, da imate nekaj kul omrežnih funkcij, na primer, da lahko naložite korenski imenik z imenom računalnika (http: //desktop/index.php), b