Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:04.

- Nazadnje spremenjeno 2025-01-23 15:08.

V tem navodilu bomo iz ničle v VHDL oblikovali glavnega vodila SPI.

1. korak: Pregled SPI

- SPI je sinhrono zaporedno vodilo

- Zaradi svoje priljubljenosti in preprostosti je bil de facto standard v serijski komunikaciji

- Polno-dupleksno vodilo

- Enostaven protokol in med najhitrejšimi serijskimi vodili

2. korak: Specifikacije oblikovanja

To so specifikacije mojstra SPI, ki jih bomo oblikovali:

- Podpira vse štiri načine delovanja; dinamično nastavljiv

- Ura omogoča varčevanje z energijo

- Statistično nastavljiva dolžina in hitrost besede

- Enkratna prekinitev za prenos in sprejem

3. korak: Zagon

Najprej bi moral imeti naš IP dva vmesnika. Eden je serijski vmesnik, drugi pa vzporedni vmesnik. Zaporedni vmesnik je sestavljen iz standardnih standardnih signalov SPI: MOSI, MISO, SS, SCLK.

MOSI se včasih imenuje SDO, MISO pa včasih SDI.

Serijski vmesnik se uporablja za komunikacijo z zunanjimi zunanjimi napravami, tj. Podrejenimi SPI.

Vzporedni vmesnik se uporablja za komunikacijo z našim gostiteljem, tj. Mikrokrmilnikom ali mikroprocesorjem, ki poveljniku pove, katere podatke je treba serijsko prenašati in prejemati prek serijskih linij. tj. Vsa podatkovna vodila pripadajo vzporednemu vmesniku.

Imamo globalno uro, ki poganja notranjo logiko SPI, in SCLK, ki ga ustvarjamo interno.

Imamo tudi nekaj krmilnih signalov, na primer omogočanje pisanja, omogočanje ure. In prekinitveni in drugi signali stanja.

Ker se moramo spoprijeti s kompleksnimi pogoji upravljanja, je takšne IP -je za serijsko komunikacijo lažje oblikovati kot FSM. SPI master bomo oblikovali tudi kot FSM. FSM bo poganjala druga notranja ura, ki je dvakrat SCLK. Ta notranja ura se ustvari s sinhronimi števci globalne ure.

Vsi nadzorni signali, ki imajo domene z navzkrižno uro, imajo sinhronizatorje, da so na varnejši strani.

4. korak: RTL pogled na glavno jedro SPI in simulacijske valovne oblike

Je gola RTL zasnova brez namenskih IP FPGA. Zato je popolnoma prenosljiva koda za kateri koli FPGA.

Priporočena:

Oblikovanje preprostega štirismernega sklopa krmilnika pridruženega predpomnilnika v VHDL: 4 koraki

Oblikovanje preprostega štirismernega nabora krmilnika pridruženega predpomnilnika v VHDL: V mojem prejšnjem navodilu smo videli, kako oblikovati preprost krmilnik predpomnilnika z neposrednim preslikavo. Tokrat gremo korak naprej. Oblikovali bomo preprost štirismerno nastavljen asociativni krmilnik predpomnilnika. Prednost? Manjša stopnja zamud, a za ceno perfo

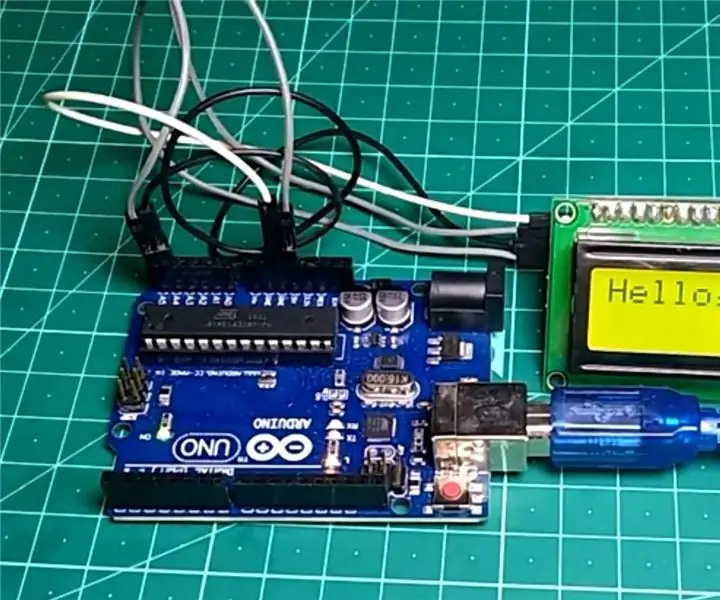

I2C / IIC LCD zaslon - Uporabite SPI LCD za LCD zaslon I2C z uporabo modula SPI do IIC z Arduinom: 5 korakov

I2C / IIC LCD zaslon | Uporabite SPI LCD za LCD zaslon I2C z uporabo modula SPI do IIC z Arduinom: Pozdravljeni, saj ima navaden SPI LCD 1602 preveč žic za povezavo, zato ga je zelo težko povezati z arduinom, vendar je na trgu na voljo en modul, ki lahko pretvorite zaslon SPI v zaslon IIC, tako da morate priključiti samo 4 žice

Oblikovanje I2C Master v VHDL: 5 korakov

Oblikovanje I2C Master v VHDL: V tem navodilu je obravnavano Oblikovanje preprostega I2C masterja v VHDL. OPOMBA: kliknite na vsako sliko za ogled celotne slike

Oblikovanje UART v VHDL: 5 korakov

Zasnova UART v VHDL: UART pomeni univerzalni asinhronski sprejemni oddajnik. To je najbolj priljubljen in najpreprostejši protokol serijske komunikacije. V tem navodilu se boste naučili, kako oblikovati modul UART v VHDL

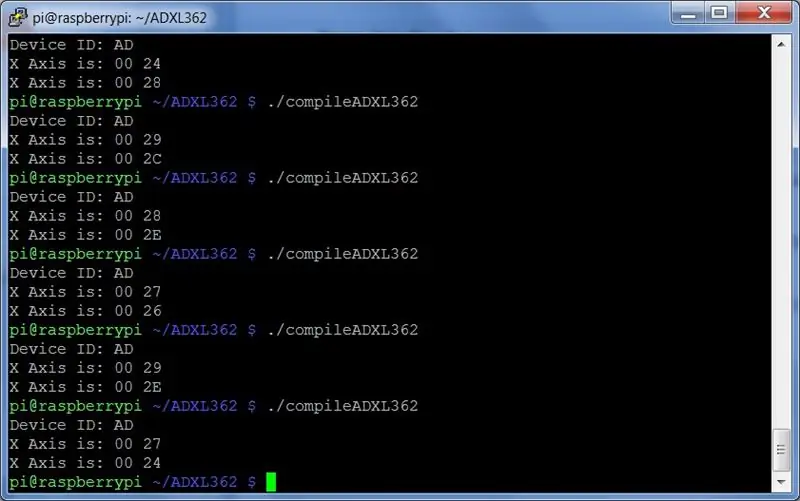

Predhodni* SPI na Pi: Komuniciranje s 3-osnim merilnikom pospeška SPI z uporabo Raspberry Pi: 10 korakov

Predhodni* SPI na Pi: Komuniciranje s 3-osnim merilnikom pospeška SPI z uporabo Raspberry Pi: Navodila po korakih za nastavitev Raspbiana in komuniciranje z napravo SPI z uporabo bcm2835 knjižnice SPI (NE bit udarjena!) To je še vedno zelo predhodno … Moram dodati boljše slike fizične povezave in obdelati nekaj nerodne kode