Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:07.

- Nazadnje spremenjeno 2025-01-23 15:09.

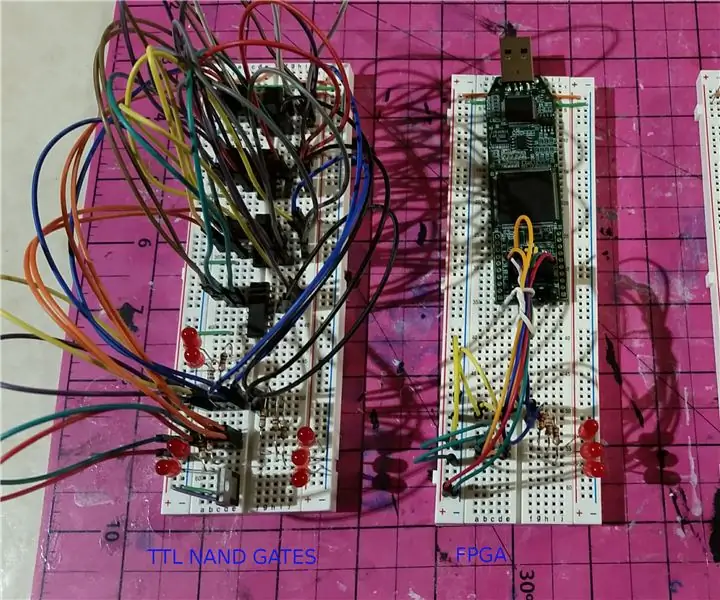

Oblikovanje strojnih logičnih vezij je lahko zabavno. Stari način šole je bil to z vrati NAND, na deski za kruh, ožičen s skakalnimi žicami. To je še vedno mogoče, vendar ne traja veliko, preden se število vrat umakne nadzoru. Novejša možnost je uporaba FPGA (Field Programmable Gate Array). Ti čipi se lahko pretvorijo v katero koli digitalno logično vezje, ki ga lahko oblikujete, vendar niso poceni in so na voljo. Pokazal bom, kako je mogoče to FPGA zamenjati s poceni čipom Atmega iz Arduino UNO, ki digitalno vezje učinkovito postavi v paket DIP, ki je zelo prijazen do plošč.

1. korak: Oblikujte vezje, ki ga bo predstavljal "FPGA"

Zgradil bom 2 -bitni + 2 -bitni seštevalnik. Potrebuje dva para logičnih vhodnih zatičev in odda tri tropetine izhodnih zatičev.

Če želite to narediti z vrati NAND, si oglejte shemo na sliki. Potrebuje 14 vrat NAND. Uporabil sem 4 štirikratne čipe NAND gate TTL in jih povezal na ploščo za kruh.

Dodal sem nekaj LED (ne pozabite na trenutne omejevalne upore), da pokažete, kdaj so bili vhodni in izhodni zatiči vklopljeni (visoko) in kdaj izklopljeni (nizko). Za pogon vhodnih zatičev sem jih preskočil na ozemljitveno tirnico ali na pozitivno vodilo.

To vezje deluje, vendar že zajema 4 čipe TTL in je podganino gnezdo žic. Če bi potrebovali več kosov, bi bilo več plošč za kruh in več skakalcev. Zelo hitro bi velikost vezja ušla izpod nadzora.

Po drugi strani pa pri delu z vrati TTL ne oddajajo natančno 0V ali 5V, kot bi pričakovali. Pogosto oddajajo okoli 3V za "visoko", vendar je natančna napetost v zelo širokem območju. Isto vezje z enakovrednimi čipi CMOS bi imelo bolje natančno 0V do točno 5V nihanje.

2. korak: Vnesite FPGA

FPGA je fantastičen čip, ki lahko dobesedno postane vsaka kombinacija logičnih vrat, povezanih v kateri koli kombinaciji. Eden oblikuje "vezje" v jeziku za strojno opremo (HDL). Obstaja več takih jezikov, od katerih se eden imenuje Verilog. Datoteka.v na sliki je ekvivalent Veriloga dvobitnega seštevalnika. Datoteka.pch pod njo je potrebna tudi za dodelitev vhodnih in izhodnih zatičev, imenovanih v datoteki verilog, resničnim zatičem strojne opreme na čipu.

V tem primeru uporabljam razvojno ploščo iCEstick Lattice Semiconductors (https://www.latticesemi.com/icestick). Dejanski čip FPGA je iCE40HX-1k z nekaj več kot 1000 vrati, ki lahko vsaka postanejo vsa logična vrata. To pomeni, da so vsa vrata lahko vrata NAND ali vrata OR, NE vrata, NOR, XOR itd. Poleg tega lahko vsa vrata pokrivajo več kot dva vhoda. To je značilno za vsakega proizvajalca, vendar lahko na vratih iCE40 vsaka vrata upravljajo s 4 vhodi. Tako so vsa vrata veliko bolj zmogljiva od dveh vhodnih vrat NAND.

Moral sem dodeliti 4 vhodne borove in 3 izhodne nožice fizičnim zatičem 91, 90, 88, 87, 81, 80 in 79. To je značilno za čip fpga in odklopno ploščo, na kateri je, in kako so ti zatiči priključeni na vrata PMOD. To je na voljo v podatkovnih listih za to ploščo FPGA.

Lattice ponuja lastno verigo orodij za sintezo (FPGA ekvivalent kompilacije za CPE) vezij iz Veriloga, vendar sem uporabil brezplačno odprtokodno verigo orodij icestorm (https://www.clifford.at/icestorm/). Navodila za namestitev so na voljo na tem spletnem mestu. Z nameščeno ledeno nevihto in datoteko verilog in pcf so ukazi za nalaganje tega vezja na FPGA naslednji:

yosys -p "synth_ice40 -blif twoBitAdder.v" twoBitAdder.blif

arachne -pnr -d 1k -p iCEstick.pcf twoBitAdder.blif -o twoBitAdder.asc

ledeni paket twoBitAdder.asc twoBitAdder.bin

iceprog twoBitAdder.bin

To deluje odlično, vendar bo dostava tega iCEstick -a stala približno 30 USD. To ni najcenejši način za izgradnjo digitalnega vezja, vendar je močan. Ima več kot 1000 vrat in za to majhno vezje uporablja le 3 od njih. Ekvivalent vrat NAND je uporabljal 14 vrat. To je posledica dejstva, da lahko vsaka vrata postanejo kakršna koli vrata, vsaka vrata pa so pravzaprav 4 vhodna vrata. Vsaka vrata lahko naredijo več. Če potrebujete več vrat, ima iCEstick večjega brata z 8000 vrati, kar stane približno dvakrat. Drugi proizvajalci imajo druge ponudbe, vendar je cena lahko precej visoka.

Korak: Od FPGA do Arduina

FPGA -ji so odlični, vendar so lahko dragi, težko jih je najti in niso zelo prijazni. Cenen in poceni čip Atmega 328 P je na voljo v lepem paketu DIP, ki je kot nalašč za izdelavo kroga. Lahko ga dobite tudi za približno 4 USD. To je srce Arduino UNO. Seveda bi lahko uporabili celoten UNO, vendar poceni, lahko odstranimo Atmego 328 P z UNO in ga uporabimo sami. Vseeno sem ploščo UNO uporabljal kot programer za Atmego.

Na tej točki boste potrebovali

1. Arduino UNO z odstranljivim procesorjem Atmega 328P.

2. Druga Atmega 328P z vnaprej zažganim zagonskim nalagalnikom Arduino, ki bo nadomestil tistega, ki ga nameravamo vzeti iz UNO. (Neobvezno, če še vedno želite imeti uporaben UNO).

Cilj je pretvoriti datoteko verilog v projekt arduino, ki ga je mogoče naložiti v 328P. Arduino temelji na C ++. Priročno je prevajalnik iz Veriloga v C ++, imenovan Verilator (https://www.veripool.org/wiki/verilator). Verilator naj bi uporabljali oblikovalci strojne opreme, ki morajo simulirati svoje zasnove, preden te modele predajo dragi strojni opremi. Verilator navzkrižno sestavi verilog v C ++, nato pa uporabnik zagotovi preskusni pas, ki zagotavlja simulirane vhodne signale in snema izhodne signale. Uporabili ga bomo za potrditev zasnove veriloga v Atmego 328P z verigo orodij Arduino.

Najprej namestite Verilator. Sledite navodilom na

Namestite tudi Arduino IDE in preverite, ali se lahko poveže z Arduino UNO prek USB -ja.

Uporabljali bomo isto datoteko verilog kot za FPGA, le da je treba spremeniti imena zatičev. Na začetku vsakega sem dodal podčrtaj (_). To je potrebno, ker knjižnice arduino vključujejo datoteko z glavo, ki stvari, kot so B0, B001 itd., Prevede v binarne številke. Druga imena vhodnih zatičev bi bila v redu, kot sta, vendar bi B0 in B1 povzročila neuspeh gradnje.

V imeniku, ki vsebuje twoBitAdder.v in iCEstick.pcf, zaženite naslednje:

verilator -Wall --cc twoBitAdder.v

To bo ustvarilo podimenik, imenovan obj_dir, ki vsebuje več novih datotek. Potrebujemo samo datoteke glave in cpp, VtwoBitAdder.h, VtwoBitAdder.cpp, VtwoBitAdder_Syms.h in VtwoBitAdder_Syms.cpp.

V Arduino IDE ustvarite novo skico, imenovano twoBitAdder.ino. To bo ustvarilo datoteko ino v novem imeniku, imenovanem twoBitAdder, v vašem imeniku Arduino sketchbook. Kopirajte datoteke VtwoBitAdder.h in VtwoBitAdder.cpp v to mapo twoBitAdder v mapi Arduino.

Zdaj kopirajte datoteke glave iz namestitve preverjevalnika.

cp/usr/local/share/verilator/include/verified*.

končno kopirajte v knjižnico std c ++ s strani https://github.com/maniacbug/StandardCplusplus. V skladu z njihovimi navodili za namestitev "To je nameščeno tako kot običajna knjižnica Arduino. Vsebino distribucije razpakirajte v mapo" knjižnice "pod svojo skico. Na primer, moja skica je na/home/maniacbug/Source/Arduino, zato je ta knjižnica je v/home/maniacbug/Source/Arduino/libraries/StandardCplusplus.

Po namestitvi ne pozabite ponastaviti svojega Arduino IDE."

Zdaj zamenjajte vsebino twoBitAdder.ino z vsebino, ki je navedena v tem koraku. To je preizkusni pas, ki ga preveritelj pričakuje, ki nastavi vhodno/izhodne zatiče, nato v zanki, prebere vhodne zatiče, jih posreduje v VtwoBitAdder (prevedena različica našega vezja), nato prebere izhode iz VtwoBitAdder in uporabi jih do izhodnih zatičev.

Ta program bi moral zbrati in izvesti na Arduino UNO.

4. korak: Od Arduina do DIP čipa na plošči za kruh

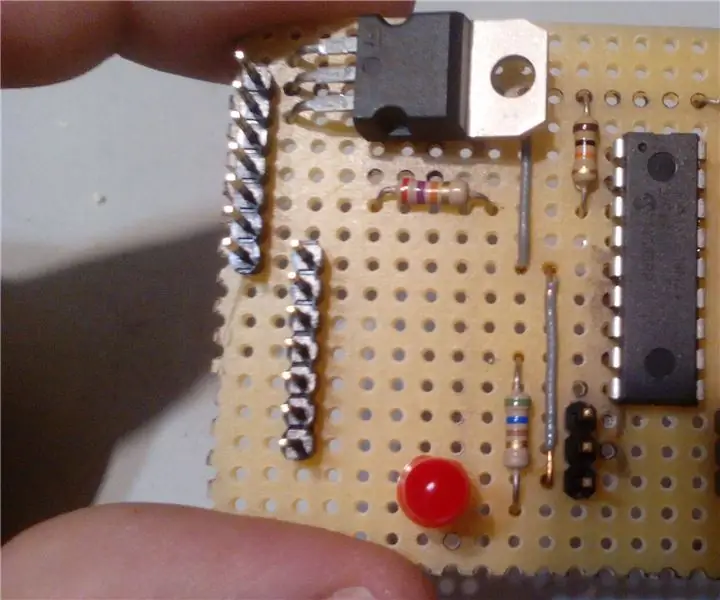

Zdaj, ko se program izvaja na Arduinu, ne potrebujemo več same plošče Arduino. Vse kar potrebujemo je CPE.

Atmego 328P previdno odstranite iz vtičnice Arduino UNO in po izbiri vstavite njeno zamenjavo.

Atmego 328P postavite na mizo. Konec postavite s krožnikom navzgor na deski za kruh. Pin 1 je zgornji levi zatič. Pin 2 je naslednji navzdol in tako naprej do pin 14, ki je spodaj levo. Nato je pin 15 spodaj desno, zatiči od 16 do 28 pa štejejo nazaj na desno stran čipa.

Zatiča 8 in 22 povežite z maso.

Priključite pin 7 na VCC (+5V).

Med zatiči 9 in 10. Povežite 16 MHz kremenčev kristal. Prav tako majhen kondenzator (22pF) med zatičem 9 in maso ter med zatičem 10 in maso. To daje Atmegi 328P takto 16Mhz. Drugje obstajajo navodila, kako 328P naučiti, da namesto tega uporablja svojo notranjo 8Mhz uro, kar bi prihranilo nekaj delov, vendar bi to upočasnilo procesor.

Vrata Arduino GPIO 5, 6, 7 in 8, ki smo jih uporabili za vhodne zatiče, so pravzaprav fizični zatiči 11, 12, 13, 14 na Atmegi 328P. To bi bili štirje spodnji zatiči na levi.

Vrata Arduino GPIO 11, 10 in 9, ki smo jih uporabili za izhodne zatiče, so pravzaprav fizični zatiči 17, 16, 15 na Atmegi 328P. To bi bili spodnji trije zatiči na desni.

LED sem na te zatiče priključil kot prej.

5. korak: Zaključek

Čipi TTL delujejo, vendar jih je za izdelavo kar nekaj potrebno. FPGA delujejo zelo dobro, vendar niso poceni. Če lahko živite z manj IO zatiči in nižjo hitrostjo, je morda čip za vas Atmega 328P.

Nekaj stvari, ki jih morate upoštevati:

FPGA:

Pro

- Zmore signale visoke hitrosti. Ker ni procesorja, ki bi obdeloval ozka grla do enega ukaza naenkrat, je omejevalni dejavnik zakasnitev širjenja skozi vrata na danem vezju. V mnogih primerih je to lahko veliko hitreje od ure, ki je priložena čipu. Za mojo zasnovo bi izračunana zakasnitev omogočila, da se twoBitAdder odzove na približno 100 milijonov sprememb vhodnih vrednosti na sekundo (100 MHz), čeprav je vgrajena ura le kristal 12 MHz.

- Ker postaja načrtovanje vse bolj zapleteno, se zmogljivost obstoječih vezij ne poslabša (veliko). Ker dodajanje vezij v tkanino preprosto vnese nekaj novega v neuporabljene nepremičnine, to ne vpliva na obstoječa vezja.

- Odvisno od FPGA je lahko število razpoložljivih vhodno -izhodnih zatičev zelo veliko in praviloma niso vezani na noben poseben namen.

Con

- Lahko je drago in/ali težko dostopno.

- Običajno je na voljo v paketu BGA, ki za delo z čipom v katerem koli amaterskem projektu potrebuje nekakšno odklopno ploščo. Če ga vgrajujete v zasnovo z večplastno SMT PCB po meri, to ni problem.

- Večina proizvajalcev FPGA ponuja lastno programsko opremo za oblikovanje zaprte kode, ki lahko v nekaterih primerih stane ali pa ima datum veljavnosti licence.

Arduino kot FPGA:

Pro

- Poceni in enostavno dostopno. Samo poiščite atmega328p-pu na Amazonu. Stanejo približno 4 USD/kos. Več prodajalcev jih prodaja v lotu po 3 ali 4.

- To je paket DIP, kar pomeni, da se popolnoma prilega ploščici z zunanjimi zatiči.

- To je 5V naprava, ki olajša povezovanje z drugimi 5V napravami.

Con

- ATMEGA328P ima omejeno število vhodov IO (23), več pa jih je rezerviranih za posebne naloge.

- Ko se zapletenost vezja povečuje, se količina kode, ki se izvaja v metodi Arduino zanke, povečuje, kar pomeni, da je trajanje vsakega cikla daljše.

- Tudi če je kompleksnost tokokroga nizka, vsak cikel zahteva veliko navodil procesorja za pridobitev vrednosti vhodnega zatiča in zapis vrednosti izhodnega zatiča ter vrnitev na vrh zanke. Z 16Mhz kristalom, tudi pri enem navodilu na cikel takta, zanka ne bo tekla več kot 1 milijon krat na sekundo (1Mhz). Za večino amaterskih elektronskih projektov je to precej hitreje, kot je potrebno.

Priporočena:

Moje CR10 novo življenje: matična plošča SKR in Marlin: 7 korakov

Moje CR10 New Life: SKR Mainboard in Marlin: Moja standardna plošča MELZI je bila mrtva in potreboval sem nujno zamenjavo, da bi oživil svoj CR10. Prvi korak, izberite nadomestno ploščo, zato sem izbral Bigtreetech skr v1.3 je 32 -bitna plošča z gonilniki TMC2208 (s podporo za način UART

SONČNA PLOŠČA KOT Sledilnik senc: 7 korakov (s slikami)

SONČNA PLOŠČA kot sledilnik senc: Temeljna velikost, ki se uporablja v fiziki in drugih znanostih za opis mehanskega gibanja, je hitrost. Merjenje je bila ponavljajoča se dejavnost v poskusnih razredih. Običajno uporabljam video kamero in programsko opremo TRACKER za preučevanje gibanja certa

Poceni in lahka robotska plošča s serijskim kablom: 12 korakov (s slikami)

Poceni in enostavna robotska plošča PICAXE s serijskim kablom: Tukaj so navodila, kako zgraditi enostavno, preprosto in poceni ploščo PICAXE za nadzor nad SUMO ROBOTOM ali za uporabo pri poljubnem številu drugih projektov PICAXE 18M2+

UDuino: Razvojna plošča, združljiva z Arduinom, zelo poceni: 7 korakov (s slikami)

UDuino: Zelo nizki stroški Arduino združljiva razvojna plošča: Arduino plošče so odlične za izdelavo prototipov. Vendar pa postanejo precej dragi, če imate več sočasnih projektov ali potrebujete veliko krmilnih plošč za večji projekt. Obstaja nekaj odličnih in cenejših alternativ (Boarduino, Freeduino), toda

Poceni (kot v brezplačnem [kot v pivu]) stojalo z več metri: 4 koraki

![Poceni (kot v brezplačnem [kot v pivu]) stojalo z več metri: 4 koraki Poceni (kot v brezplačnem [kot v pivu]) stojalo z več metri: 4 koraki](https://i.howwhatproduce.com/images/004/image-11898-43-j.webp)

Poceni (kot v brezplačnem [kot v pivu]) večmetrsko stojalo: motilo me je, da moram dvigniti vrat ali negotovo uravnotežiti svoj poceni večmetrski 4 USD, kjer lahko dejansko preberem zaslon. Zato sem se odločil, da vzamem stvari v svoje roke! To je tudi moja prva "strukturirana", zato če ima kdo koristne komentarje