Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:02.

- Nazadnje spremenjeno 2025-01-23 15:07.

V preteklosti sem napisal vodnik o tem, kako zgraditi računalnik na osnovi Z80, in vezje sem oblikoval tako, da je čim bolj poenostavljen, da ga je mogoče čim lažje zgraditi. Napisal sem tudi majhen program z isto idejo preprostosti. Ta zasnova je delovala precej dobro, vendar nisem bil popolnoma zadovoljen z njo. Začel sem s prepisovanjem programa, ki je omogočal programiranje med izvajanjem. To mi je omogočilo, da preizkusim kode, ne da bi jih bilo treba posvetiti EEPROM -u, kar bi posledično zahtevalo, da ponovno programiram EEPROM. To se mi ni zdelo zabavna ideja. Potem sem začel razmišljati o spominskih prostorih. Če bi želel povezati vmesnik strojne opreme (predvsem IO), bi lahko koda potencialno presegla količino pomnilniškega prostora, ki je na voljo sistemu. Ne pozabite, da je zasnova uporabljala samo spodnji bajt naslovnega vodila, nato pa je bil spodnji bit visokega bajta uporabljen za izbiro med prostori ROM in RAM. To je pomenilo, da imam na voljo le 253 bajtov prostora. Morda se sprašujete, zakaj 253 namesto 256. To je zato, ker moja nova koda vbrizga tri bajte podatkov na koncu pisnega programa (to bo obravnavano kasneje, ko sem ga spremenil za delo na novi zasnovi).

n

Vrnil sem se po starih shemah, da vidim, kaj se še dogaja. Pri vezju za izbiro pomnilnika sem našel majhno napako, ki jo bom pokril, ko pridem tja. Poenostavljena različica: vse zahteve za pisanje bi dejansko potekale, čeprav so bile vedno vstavljene v RAM. Verjetno zaradi tega ni bilo treba skrbeti, vendar sem tokrat želel narediti pravilno. In s tem sem začel risati novo shemo. Dve sliki, priloženi tej strani, sta pred in po dejanskem vezju. Počistil sem toliko ožičenja špagetov, da ni smešno.

n

Če ste sledili moji prvotni oddaji in nameravate slediti tej, me boste sovražili. Če začenjate na novo, potem imate srečo. Samo vzemite dele na seznamu (ali njihov enakovreden) in sledite.

Zaloge:

LM7805 - 5 -voltni regulator Z80 - CPE; možgane sistema AT28C64B - EEPROM. »Trajno« shranjevanje podatkov, ki se uporablja za vdelano programsko opremo računalnika IDT6116SA - SRAM; uporablja se za shranjevanje uporabniške kode in /ali splošnega shranjevanja podatkovNE555 - sistemska ura74HC374 - osminska zaponka D z /OE; uporablja se kot vhodni čip74LS273 - oktalni D -zapah z /MR; izhodni čipTLC59211 - LED gonilniški čip (uporabljen tako, da lahko 74LS273 poganja LED, saj sam ne zmore trenutnega izhoda) MC14572 - To je čip "Line Driver", vendar se mi je zdel popoln za logiko upravljanja pomnilnika. Ima 4 pretvornike in vrata NAND in NOR, vgrajena 74LS32 - štirikratna ALI vrataCD4001 - štirikratna vrata NOR CD4040 - 12 -stopenjski števec valov; Vlečen, vendar ne izveden delilnik ure (za delovanje sistema pri počasnejših urah) 2 10K ohmski upori - eden se uporablja v časovnem vezju 555, zato za to uporabite poljubno vrednost 4 1 ohmski upori - eden se uporablja za 555 časovno vezje, zato uporabite kar želite. Druga se uporablja za pogon LED, zato jo spremenite tudi, če želite 8x330 ohmsko uporno vodilo 8 x 10 k ohmsko uporno vodilo11 LED - tri se uporabljajo za stanje sistema, preostalih osem pa je izhod. Za 8 sem uporabil prikaz črtnega grafa (HDSP -4836) 4 kondenzatorja - dva sta uporabljena LM7805; 0,22 uF in 0,1 uF. Eden je za časovnik 555, zato uporabite tisto, kar menite, da je prav. Zadnji je za ponastavitev ob vklopu; 100uF2 N. O. Potisni gumbi - Eden se uporablja za vnos, drugi za ponastavitev 8 SPST DIP stikala - Vnos podatkov; Uporabil sem Piano Key style styleWire. Veliko in veliko žice

n

OPOMBA: Različica MC14572 skozi luknjo je zastarela, vendar je različica SMD še vedno aktivna (niti v statusu "ni za novo zasnovo"), zato boste morda morali kupiti vezje, ki vam bo omogočilo njeno uporabo. Namesto MC14572 lahko uporabite drugi 74LS32 (glejte shemo "vezja za izbiro pomnilnika" prejšnje ible)

1. korak: hiter pregled sprememb + sheme

Kako prebrati sheme: Puščica, usmerjena v čip, je vhod: Vhod> -Puščica, usmerjena stran od čipa, je izhod: Izhod <-Vodniki namesto puščice uporabljajo črto: Bus |-

n

Večina žetonov je izžrebanih z natančnimi izpiski. Na teh žetonih je bilo narejeno malo padca. Večina čipov ima tudi številke pin in nalepke. Morda jih je težko brati. Moj svinčnik je postajal dolgočasen.

n

Z vidika povezav vezja je postavitev nove zasnove večinoma nespremenjena v primerjavi s prvotno. Spodnji griz naslova visokega bajta sem povezal s pomnilniki, nato pa za izbiro RAM/ROM uporabil spodnji bit zgornjega gnezda (A12). To je pomenilo, da je prostor ROM-a od 0000-00FF do 0000-0FFF. Ram prostor je šel od 0100-01FF do 1000-1FFF. Logiko Memory Control sem zamenjal tudi za boljši dizajn in dodal dve novi LED diodi stanja (in nekaj logike lepljenja). Narisala sem (vendar nisem ožičila) vezja delilnika ure. Izvajati naj bi dve funkciji. Očitna funkcija je deljenje časovne frekvence navzdol. Druga funkcija je za PWM (Pulse Width Modulation), saj 555 ne ustvarja valov s 50% obratovalnimi cikli. To v tem vezju v resnici ni pomembno, če pa želite uro uporabiti za pogon nekaterih LED, boste zagotovo opazili učinke (ena (niz) LED (-ov) bo temnejša od druge). Ves preostali del vezja je v bistvu nespremenjen.

2. korak: CPU, pomnilnik in nadzor pomnilnika

To je del, kjer me sovražijo bralci moje prejšnje različice. V prvotni zgradbi sem nekako vrgel dele na ploščo na mesto, za katero je bilo videti, da bi imeli težave pri povezovanju. Rezultat je bil videti, kot da je nekdo nanj vrgel krožnik špagetov in je bil kot "žice!" Hotel sem ga malo počistiti, zato sem začel s kopiranjem vsega razen CPE -ja, RAM -a in ROM -a. Povlekel sem skoraj celotno vhodno vezje, izhodno vezje in logiko lepljenja. Skoraj me je bolelo, vendar je bilo potrebno. Vse podatkovne povezave sem pustil nedotaknjene in spodnji bajt naslovnega vodila. Nato sem naslednje štiri bite naslovnega vodila (A8-A11) povezal z ROM čipom. Tokrat sem skrbel, da sem šel okoli čipa, da sem ga lažje potegnil za reprogramiranje. Prav tako sem skočil naslovne povezave do čipa RAM.

n

S tem sem se moral izogniti logiki upravljanja pomnilnika. V prvotni shemi sem linijo procesorja /MREQ priključil neposredno na /CE na oba pomnilniška čipa, nato sem povezal /WR z RAM -om /WE. Potem sem imel CPU -jeve /RD in /MREQ logično ALI skupaj in tudi A9. V bistvu je bil nastavljen tako, da so vse zahteve za pomnilnik aktivirale RAM in ROM, vendar je bil A9 uporabljen za izbiro, kateri od čipov /OE je izbran. To je bilo v redu in vse zato, ker so čipi ostali neaktivni, dokler ni bila poslana zahteva po pomnilniku, nato pa bi bil med zahtevo za branje aktiven le en /OE. To je preprečilo preslušanje, vendar je prineslo neroden odtenek. Ker je bil A9 uporabljen samo za ugotavljanje, kateri čip oddaja podatke in ker je imel CPE neposreden dostop do RAM -ove /WE pin, bi šle vse in vse zahteve za pisanje. Za ROM je bilo to v redu, ker je njegov način pisanja onemogočen z vezavo /WE neposredno na napajanje 5V. RAM bi bil zapisan ne glede na A9. To je pomenilo, da bi poskus pisanja na mesto prostora ROM zapisal na isto mesto v prostoru RAM.

n

Ena od rešitev za to bi bila ponovna povezava krmilne logike, tako da ima CPE neposreden dostop do žetonov /OE in /WE zatičev, nato pa z uporabo MREQ in A12 izberite, kateri čipi /CE bodo poganjali. Šel sem s to idejo, vendar sem namesto štirih vrat NOR in pretvornika, kakršen je bil prvotni dizajn, našel neroden mali čip, ki je bil kot nalašč za to nalogo. Moral sem ustvariti vezje, ki je uporabljalo samo logična vrata, ki so na voljo v čipu, vendar je bilo to dovolj preprosto. A12 se napaja neposredno v vrata NAND in vrata NOR. /MREQ se vnese v vrata NOR, njegov kompliment pa v vrata NAND. Vrata NAND se uporabljajo za pogon /CE za RAM, izhod NOR pa se obrne in se uporablja za pogon ROM /CE. To pomeni, da mora biti /MREQ nizek, preden se izbere kateri koli čip, nato pa A12 izbere, kateri bo izbran. S to nastavitvijo zdaj nobene zahteve za pisanje v ROM ne bodo naredile ničesar. Prihrani tudi energijo, ker je namesto obeh aktiven le en čip. Kar se tiče samega logičnega čipa, imamo v notranjosti še dva neuporabljena pretvornika. Eden se bo pozneje navadil, toda prišli bomo, ko pridemo tja.

3. korak: LED diode stanja sistema

Preden sem začel s tem projektom, sem poskušal vzpostaviti povezavo z določeno IC, vendar sem imel težave z njo. Nisem prepričan, kaj se dogaja, sem uporabil LED za montažo na ploščo, da sem preiskal (eden od tistih sklopov, ki ima vgrajen upor). To mi je dalo idejo nostalgije, ki se uporablja še danes: LED -lučke stanja so pokazale, ali se pomnilnik bere ali piše v. Uporabljati ga je bilo treba skupaj z vhodno LED, ki sem jo že imel. Vhodna LED je bila povezana z generatorjem signalov /WAIT, da nam pokaže, da sistem čaka na vnos (prišel bom, ne skrbite). Razmišljal sem o tem, da bi dodal LED za označevanje IO zapisa, vendar sem ugotovil, da bi bila sprememba izhodnih LED že odličen pokazatelj tega. Če razmišljam o tem, ga lahko še dodam. Kljub temu se mi zdi koristno vedeti, ali se spomin bere ali piše. No, vseeno je uporaben za odpravljanje napak v programu. Pravzaprav sem ga močno izkoristil, ko sem poskušal spraviti program v delo: "zakaj piše v spomin? Tega še ne bi smel početi!"

n

Za nadzor teh LED sem uporabil štirikratna vrata NOR. Uporabil sem vsa vrata. Samo dva sta bila uporabljena za generiranje signalov stanja, vendar čip nima zmogljivosti napajanja za dejansko poganjanje LED. Sposobni so potopiti tolikšno moč, zato sem druga dva vrata NOR uporabil kot pretvornike in kot take priključil LED. Ker se ena LED uporablja za označevanje branja, druga pa za zapisovanje in zahteva za branje in pisanje se ne bo pojavila hkrati, sem se lahko izognil uporabi samo enega upora za obe LED. Kar se tiče signalov, ki sem jih potreboval za dekodiranje, je bilo to tudi dovolj enostavno. Želel sem, da so označene vse zahteve za branje pomnilnika, zato so imela prva vrata NOR na svojih vhodih /MREQ in /RD. Status pisanja je bil nekoliko bolj zapleten, a prav tako enostaven. Še vedno sem uporabljal /MREQ kot en vhod, vendar bi uporaba /WR kot drugega povzročila manjši odtenek, ki sem se mu želel izogniti. Navedlo bi VSE zahteve po pisanju. Hotel sem samo tiste, ki so dejansko šle skozi. Torej, kako bi to naredil? No, se spomnite, kako sem nastavil sistem, da se lahko zapiše samo RAM? Uporabil sem RAM -e /CE kot drugi vhod na vrata NOR. To pomeni, da bo LED zasvetila le, ko je izbran RAM in je podana zahteva za pisanje. Kar se tiče barve LED, sem za indikator branja izbral oranžno (vendar sem našel le rumene) in rdečo kot indikator pisanja.

4. korak: Vnos in izhod

V prejšnjem koraku ste morda opazili, da sem nekatere druge komponente že dodal na ploščo. Rezerviral sem prostor, da ne bi pomotoma postavil žic, kjer bi želel komponento (zato bi moral najti novo lokacijo za omenjeno komponento). Morda ste tudi opazili, da sem vhodna stikala pustila na mestu in ožičila do napajalne tirnice. Odločil sem se, da je prvotna lokacija odlično mesto, in odločil sem se, da bom v bližini (zgoraj) postavil izhodne LED. Desno od prikaza vrstice je vhodni zapah. Nad tem je izhodni zapah, levo od njega pa gonilnik LED. Začel sem s povezovanjem zaslona z gonilnikom, saj je bilo to najlažje. Nato sem stikala priključila na vhodno stran vhodnega zapaha. Nato sem priključil izhodno stran izhodnega zapaha na gonilnik LED. Morda se zdi to neprijetno naročilo za povezovanje teh povezav, vendar je bilo z razlogom. Vhod izhodnega zapaha naj bi bil priključen na podatkovno vodilo, pa tudi izhod vhodnega zapaha. Ideja je bila povezati izhode vhodnega zapaha z vhodi izhodnega zapaha, kar sem tudi storil. Potem sem vse, kar sem moral narediti, povezati z neredom na podatkovno vodilo. Ni bilo pomembno, kam so te povezave šle fizično, ker bi bile vse električno povezane. Računalnik je zdaj skoraj končan.

5. korak: Ponastavi in zaključi vnos in izhod

Za ta korak žal ni slik. Slike si oglejte v prejšnjem koraku.

n

Morda ste na zadnji sliki prejšnjega koraka opazili, da sem imel nameščen zeleni gumb in drug logični čip. Čip je vrata OR. Za ustvarjanje signala /WAIT se uporabljata dve vrati. No, eden generira signal z OR-ing /IORQ in /RD iz procesorja. Izhod se vnese v druga vrata, kjer se ponovno vrne na gumb. Gumb poveča vhod vrat in tako poveča izhod. Ta izhod se napaja na procesorje /WAIT pin. Medtem ko ni pritisnjen, upor drži vhod nizko. Sprva sem uporabil 10K upor, vendar je LS32 dejansko dajal napetost na vhodu. Upor ga ni spustil dovolj nizko in moral sem ga zamenjati z 1K. Kakorkoli že, ideja je, da ko je podana zahteva za branje IO, prva in druga vrata OR povedo procesorju, naj počaka. Ko nastavite vhodna stikala na karkoli želite, pritisnete gumb in CPU izklopi iz stanja čakanja. Zelena "vhodna" LED, kot sem jo poimenovala v prejšnjem koraku, je ožičena, tako da, ko se zatič /WAIT spusti, zasveti.

n

Ampak še nismo končali. Vhodna japonka potrebuje signal, da sporoči, kdaj je vnos podatkov veljaven, in jo je treba posredovati CPE -ju. Ta zatič za uro je visoko aktiven. Prej smo ga samo povezali z gumbom. To je še vedno veljavna možnost, vendar sem se tokrat odločil, da jo postavim na isti izhod kot druga vrata OR. Ta IC ima tudi pin /OE, ki ga je treba poganjati. Če bi ga držali visoko, ne bi nikoli vstavil podatkov v vodilo. Če bi ga držali nizko, bi vedno vozil avtobus. Če želite to popraviti, sem preprosto uporabil tretja vrata OR. Vhoda sta /IORQ in /RD, izhod pa gre neposredno na zapah /OE.

n

Za izhodni zapah je potreben tudi zatič ure. Spet je visoko aktiven. V svoji shemi sem narisal četrta vrata OR, ki neposredno poganjajo pin z uporabo /IORQ in /WR. To je pomenilo, da se bo nožni uro držal visoko, dokler ni podana zahteva za pisanje, nato pa se bo znižal, nato pa spet visoko. To bi bilo verjetno v redu, ker bi imelo podatkovno vodilo takoj po poskusu zapisa še vedno veljavne podatke, vendar je bilo z inženirskega vidika zasnova smeti. Te napake sem opazil šele po tem, ko sem posnel zadnje fotografije, vendar sem to povezavo prekinil in nato izhod vrat OR vstavil v enega od neuporabljenih pretvornikov iz logike upravljanja pomnilnika, nato pa njegov izhod priključil na uro.. Popravil sem tudi shemo in odkril še eno napako, ki sem jo naredil. Tudi to sem popravil.

n

Ko je bilo vse to končno opravljeno, me je čakalo zelo malo dela: vezje za ponastavitev. Na ploščo sem dodal gumb in uporabil 10K upor, da sem eno stran držal visoko. Druga stran gre neposredno na tla. Dvignjena stran je izhod /RESET, ki je šel do vsakega čipa z zatičem /RESET (CPE in izhodni zapah). Za ponastavitev ob vklopu sem na izhod /RESET dodal kondenzator. Zamisel je, da bi upor velike vrednosti povzročil, da se razmeroma velik kondenzator počasi polni in zadrži zatiče /RESET nizko za določeno število ciklov ure (CPE potrebuje štiri takte takta). Verjetno lahko že uganite, kakšna je negativna stran tega vezja. Je enak negativen kot prejšnja različica, ker je isto vezje. Ko pritisnete gumb, se kondenzator v bistvu prekine skozi gumb. To je slabo za pokrovček in gumb, zato, če želite svojo zgradbo narediti nekoliko bolj trajno, jo boste morda želeli preoblikovati. Razmišljal sem o drugem merilniku časa 555, nastavljenem v monostabilnem načinu. Toda s tem je računalniško vezje končano. Juhu. Zdaj ga je treba programirati.

6. korak: Programiranje

Programiranje te stvari je bila nočna mora. Zgradil sem Arduino EEPROM programer. Ni delovalo. Zgradil sem drugega na podlagi zasnove in kodiranja nekoga drugega. Še vedno ni delovalo. Vrnil sem se k preizkušeni metodi ročne nastavitve naslovov in podatkovnih bajtov ročno. Nekako sem to zmotil. Poskusil sem še enkrat in vseeno se je zmotilo. Še enkrat sem se vrnil in odkril, da je bil izključen za en sam bajt, zato sem ga popravil in končno je uspelo, hvala Bogu.

n

Kar zadeva dejanski program, je videti, da je zelo kompleksen in mu je težko slediti, vendar ni. Pravzaprav je precej preprosto. Polovica prepisuje številke. Drugo polovico si delijo 16-bitna matematika, pogojni skoki in še več kopiranja številk. Pa naj grem skozi to in vam povem, kako deluje.

n

Inicializacija samo nastavi nekaj vrednosti registra za uporabo v programu. Programska zanka je nekoliko bolj zapletena, vendar ne veliko. Najprej sprejme vnos v register A na vratih 00. Nato se register E zapiše v pomnilnik. V prvih dveh zankah register E vsebuje neželene podatke, zato jih poskušamo zapisati v zadnja dva bajta prostora ROM, ker dejansko ne bo zapisan; kazalec naslova (IY) se nato poveča. Vrednost, shranjena v D, se nato premakne v E, da se zapiše naprej. A se nato naloži v D in L, E pa se kopira v H. HL je primerjava vrednosti z odštevanjem in preverjanjem ZF (ničelna zastavica). Prva vrednost v primerjavi je shranjena v registrih B in C. B in C se obravnavata kot en sam 16-bitni register, BC. Če so vrednosti enake, program skoči naravnost v prostor RAM -a, kjer naj bi bila uporabniška koda. Če se koda v BC ne ujema, se HL znova naloži z začetnimi vrednostmi iz D in E in se ponovno primerja z vrednostjo v SP na enak način kot v primerjavi z BC. Če se ujema, ima enak rezultat, vendar se v pomnilnik zapišejo trije dodatni bajti. Bajti so koda, ki povzroči, da CPU skoči nazaj na sam začetek svojega programa (ponastavitev programske opreme). Če se druga primerjava ni ujemala, pa se program vrti tja, kjer od uporabnika pridobi vrednost.

n

LD SP, EDBFH; exe koda (doda skok)

n

LD IY, FFEH; kazalec začetnega pomnilnika za shranjevanje kode

n

LD BC, EDC3H; exe koda (brez zanke)

n

zanka; assembler, zato nam ni treba vedeti, kje v spominu je ta del

n

IN A, (00H); pridobite podatke o programu

n

LD (IY+00H), E; E vsebuje kodo za shranjevanje

n

INC IY; premaknite se na naslednjo pomnilniško mesto

n

LD E, D; ld D v E

n

LD D, A; ld A v D

n

LD H, E; ld E v H

n

LD L, D; ld D v L

n

ALI A; ponastavi zastavo za prevoz

n

SBC HL, BC; vrne 0, če je bila vnesena koda exe 2

n

JP Z, 1000H; če je tako, pojdite na in izvedite program

n

LD H, E; sicer jih osvežite na ustrezne vrednosti

n

LD L, D

n

ALI A; prvi odštevek je morda nastavil zastavo za prenos. Počisti

n

SBC HL, SP; vrne 0, če je bila vnesena koda exe 1

n

JP NZ, zanka; če ne, ponovite postopek (začenši s pridobivanjem vrednosti)

n

LD (IY+00H), C3H; v nasprotnem primeru vnesite kodo za skok na koncu uporabniškega programa

n

LD (IY+01H), 00H; jump v bistvu deluje kot ponastavitev programske opreme

n

LD (IY+02H), 00H; to je popolna ponastavitev v primeru spreminjanja registrov

n

JP 1000H; skočite in zaženite uporabniški program

Priporočena:

Nastavitev Raspberry Pi 4 prek prenosnega računalnika/računalnika z uporabo Ethernetnega kabla (brez monitorja, brez Wi-Fi): 8 korakov

Nastavitev Raspberry Pi 4 prek prenosnega računalnika/računalnika z uporabo Ethernetnega kabla (brez monitorja, brez Wi-Fi-ja): Pri tem bomo za nastavitev delali z Raspberry Pi 4 Model-B z 1 Gb RAM-a. Raspberry-Pi je enosmerni računalnik, ki se uporablja za izobraževalne namene in DIY projekte po dostopni ceni, zahteva napajanje 5V 3A

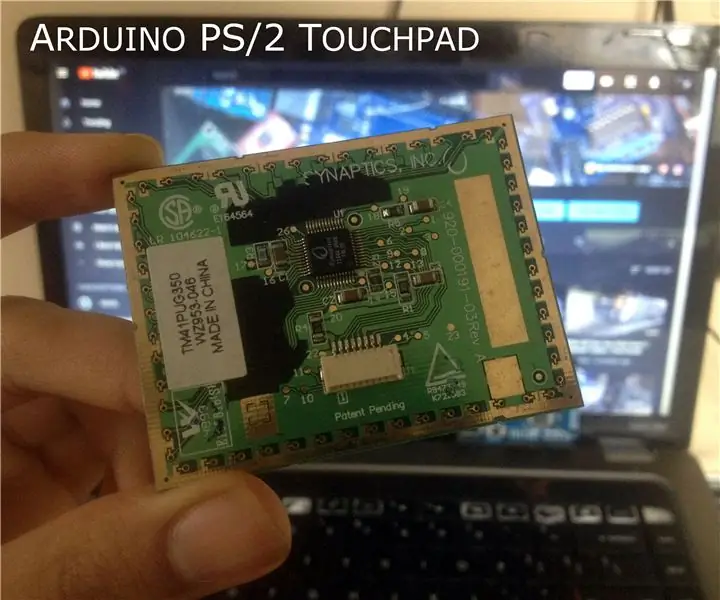

Za upravljanje računalnika znova uporabite sledilno ploščico starega prenosnega računalnika!: 11 korakov (s slikami)

Znova uporabite sledilno ploščico starega prenosnega računalnika za nadzor računalnika!: Sledilne ploščice prenosnega računalnika PS/2 so med najbolj kul napravami uporabniškega vmesnika za uporabo z mikrokrmilnikom. Z drsnimi in dotikalnimi kretnjami prstov lahko na preprost in zabaven način nadzorujete stvari. V tem navodilu združimo eno z

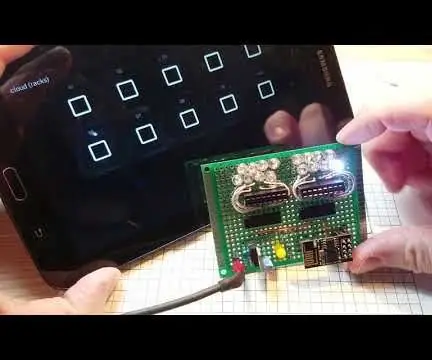

Oddaljeni izklop ali ponovni zagon računalnika z napravo ESP8266: 10 korakov (s slikami)

Oddaljeni izklop ali ponovni zagon računalnika z napravo ESP8266: Če želite biti jasni, zapiramo VAŠ računalnik in ne računalnik nekoga drugega. Zgodba gre takole: Moj prijatelj na Facebooku mi je poslal sporočilo in rekel, da ima na ducatu računalnikov kup matematike, vendar se vsako jutro ob treh zjutraj zaklenejo. S

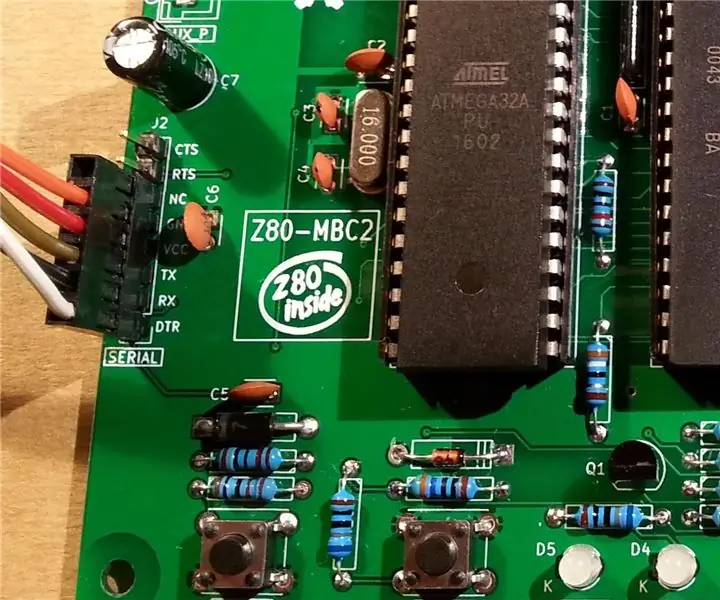

Enostaven za izdelavo pravega domačega računalnika: Z80-MBC2!: 9 korakov (s slikami)

Pravi domači računalnik, ki ga je enostavno zgraditi: Z80-MBC2 !: Če vas zanima, kako računalnik deluje in deluje z " zunanjimi stvarmi ", je dandanes na voljo veliko plošč, kot so Arduino ali Raspberry in mnoge druge. Toda te plošče imajo enako "omejitev" … zdravo

Izklop, ponovni zagon ali mirovanje računalnika po urniku: 6 korakov

Zaustavitev, ponovni zagon ali mirovanje računalnika po urniku: V tem navodilu vam bom pokazal, kako računalnik po urniku zaustavite, znova zaženete ali preklopite v mirovanje. Glejte obvestilo na koncu, če uporabljate starejši operacijski sistem kot Windows XP