Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:02.

- Nazadnje spremenjeno 2025-01-23 15:08.

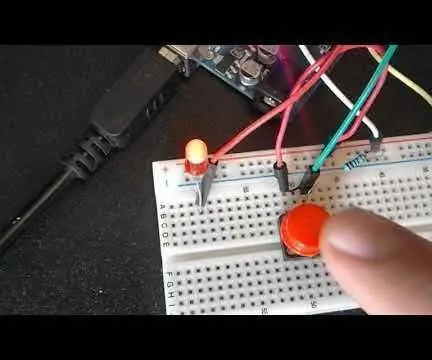

V tej vadnici bomo uporabili FPGA za nadzor zunanjega LED vezja. Izvajali bomo naslednje naloge

(A) Za upravljanje LED uporabite tipke na FPGA Cyclone IV DuePrologic.

(B) LED dioda bliskavice se občasno vklopi in izklopi

Video demo

Laboratorijski meni:

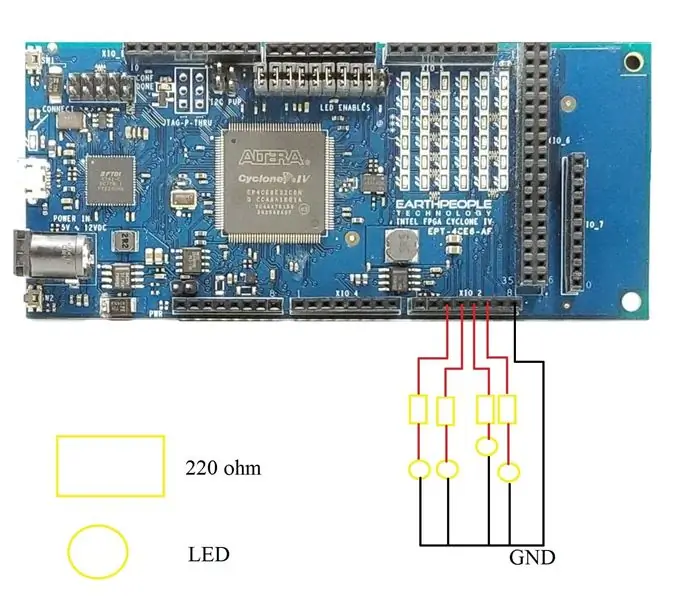

Korak: Zgradite elektronsko vezje

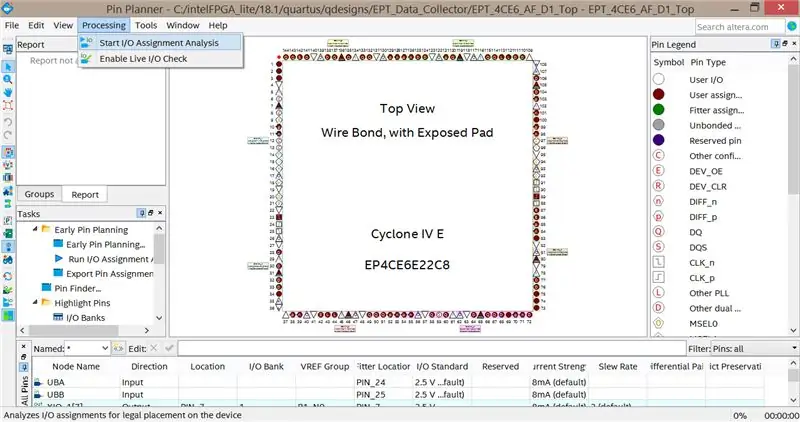

2. korak: Preverite načrtovalec zatičev in uredite verilog kodo

3. korak: Uredite verilog kodo

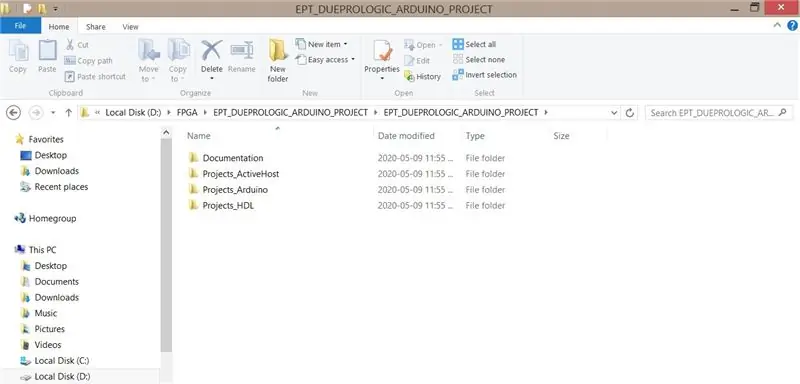

Ko kupite FPGA DueProLogic, morate prejeti DVD. Ko odprete »Projects_HDL«, bi morali videti izvirno kodno datoteko

Dodajte označeno kodo. Registrira V/I vrata in dodeljuje številke vhodom.

izhodna žica [7: 0] XIO_1, // XIO-D2-D9

izhodna žica [5: 0] XIO_2, // XIO-D10-D12

izhodna žica [5: 0] XIO_3, // XIO-D22-D29

vhodna žica [5: 0] XIO_4, // XIO-D30-D37

vhodna žica [5: 0] XIO_5, // XIO-D38-D45

izhodna žica [4: 0] XIO_6_OUT, // XIO-D46-D53

vhodna žica [31: 5] XIO_6, // XIO-D46-D53

izhodna žica [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

vhodna žica UBA, // Stikala s pritiskom na gumb

vhodna žica UBB // Stikala za stikala

dodeli XIO_1 [3] = start_stop_cntrl;

dodeli XIO_2 [1] = start_blinky; // LED bliskavica LED vklopljena in izklopljena

dodeli XIO_2 [2] = 1'b1; // izhod HIGH

dodeli XIO_2 [3] = ~ UBA; // Pritisnite gumb A

dodelite XIO_2 [4] = UBB; // Pritisnite gumb B

dodeli c_enable = XIO_5 [2];

dodeli LEDExt = XIO_5 [5];

Nato moramo nastaviti časovni zamik. Komentirajte prvotno kodo časovnika in napišite novo funkcijo časovnika

//-----------------------------------------------

// LED utripajoč zagon

//-----------------------------------------------

/*

vedno @(postavljeno CLK_66 ali negedge RST)

začeti

če (! RST)

start_blinky <= 1'b0;

drugače

začeti

če (control_register [7: 4]> 0)

start_blinky <= 1'b1;

drugače

start_blinky <= 1'b0;

konec

konec

*/

reg [31: 0] ex;

začetni začetek

ex <= 32'b0;

start_blinky <= 1'b0;

konec

vedno @(postavljeno CLK_66)

začeti

ex <= ex + 1'b1;

if (ex> 100000000) // vklop/izklop bliskavice ~ 1,6 sekunde, ura 66MHz

začeti

start_blinky <=! start_blinky;

ex <= 32'b0;

konec

konec

//-----------------------------------------------

// Števec merilnika zakasnitve LED

//-----------------------------------------------

/*

vedno @(postavljeno CLK_66 ali negedge RST)

začeti

če (! RST)

števec led_delay_ = <TIMER_LOW_LIMIT;

drugače

začeti

če (navedite [SELECT_MODE])

števec led_delay_counter <= timer_value;

drugače če (navedite [WAIT_FOR_TIMER])

števec led_delay_counter <= led_delay_counter - 1'd1;

konec

konec*/

4. korak: Sestavite Verilog kodo

Pritisnite "Začni kompilacijo" v Quartusu, sporočilo o napaki ne sme biti ustvarjeno.

Če prejmete sporočilo o napaki o več zatičih. Pojdite na Naloge -> Naprava -> Možnosti naprave in zatičev -> Dvonamenski zatiči -> spremenite vrednost ustreznega zatiča na "Uporabi kot običajen V/I".

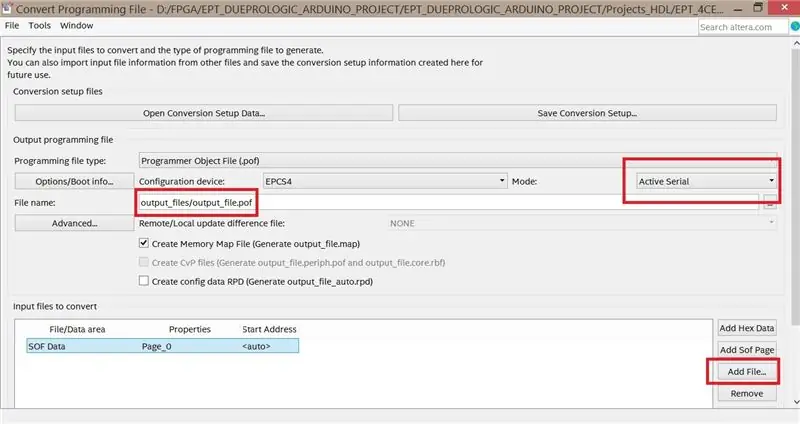

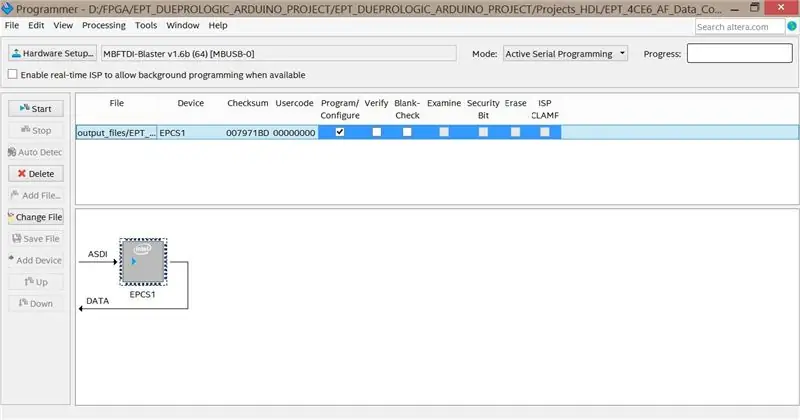

Po kompilaciji bi morali dobiti pof izhodno datoteko neposredno. Če vaša programska oprema ni posodobljena, lahko dobite samo sof datoteko. Ko se to zgodi, kliknite "Datoteka" v Quartusu -> "pretvori programske datoteke". Spremenite nastavitve, označene z rdečimi polji.

5. korak: Poskusimo

Konec koncev bi moralo delovati !!! Rumena LED sveti vedno. Rdeča LED utripa. Modra LED se izklopi, če pritisnete gumb B. Zelena LED se vklopi, če pritisnete gumb A

Priporočena:

Gumb vrtljivega dajalnika: 6 korakov

Gumb za rotacijski dajalnik: To je rotacijski daljinski upravljalnik, ki temelji na rotacijskem kodirniku. Ima naslednje funkcije: Baterija deluje z zelo nizko porabo toka, ko je aktivirana Samodejno aktiviranje, ko se krmiljenje vrti Samodejno spanje po obdobju nedejavnosti Konfiguriraj

FPGA Cyclone IV DueProLogic nadzoruje kamero Raspberry Pi: 5 korakov

FPGA Cyclone IV DueProLogic nadzoruje kamero Raspberry Pi: Kljub temu, da je FPGA DueProLogic uradno zasnovan za Arduino, bomo omogočili komunikacijo FPGA in Raspberry Pi 4B. V tej vadnici so izvedene tri naloge: (A) Hkrati pritisnite dva gumba na FPGA za obrnitev kota

Servo motor FPGA Cyclone IV DueProLogic nadzoruje: 4 korake

Servo motor FPGA Cyclone IV DueProLogic Controls: V tej vadnici bomo napisali Verilog kodo za krmiljenje servo motorja. Servo SG-90 proizvaja Waveshare. Ko kupite servo motor, boste morda prejeli podatkovni list, ki vsebuje delovno napetost, največji navor in predlagani Pu

Visuino Kako uporabljati gumb kot vhod za nadzor stvari, kot je LED: 6 korakov

Visuino Kako uporabljati gumb kot vhod za nadzor stvari, kot je LED: V tej vadnici se bomo naučili, kako vklopiti in izklopiti LED z enostavnim gumbom in Visuinom. Oglejte si predstavitveni video

LED, s pritiskom na gumb Start in Fade Out: 5 korakov

LED, s pritiskom na gumb Start in Fade Out: To bo opisalo preprosto vezje, ki omogoča, da 9 v. Baterija napaja LED, nato pa po izklopu gumba izgine. Nekaj zelo podobnega je bilo zahtevano v nekem vprašanju na forumih. Upam, da je to uporabno kot prototip,