Kazalo:

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:04.

- Nazadnje spremenjeno 2025-01-23 15:08.

Naš cilj s tem projektom je bil ustvariti nekaj, kar bi skupnosti prihranilo energijo in finančne vire. Ulične luči, ki jih aktivira gibanje, bi naredile obe stvari. Po vsej državi se energija troši na ulične luči, ki osvetljujejo prazne ulice. Naš sistem ulične razsvetljave zagotavlja, da luči prižgejo le, kadar je to potrebno, skupnosti pa prihrani nešteto dolarjev. S senzorji gibanja sistem prižge luči le, ko so prisotni avtomobili. Tudi za varnost pešcev smo uvedli gumb za preglasitev, ki prižge vse luči na ulici. Naslednji koraki vas bodo vodili skozi to, kako smo zasnovali in zgradili naš pomanjšani model projekta z uporabo Vivada in plošče Basys 3.

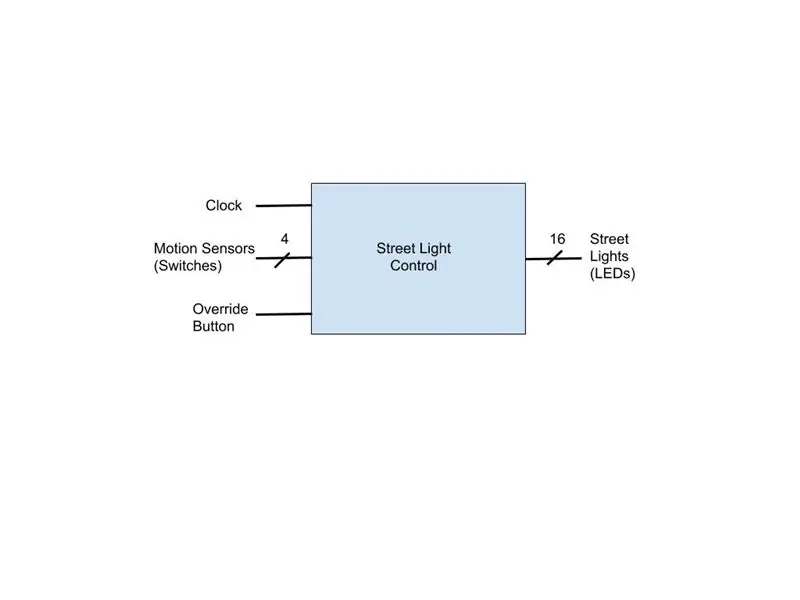

Korak: Sistemska črna škatla

Ta projekt smo začeli z risanjem preprostega diagrama črne škatle. Diagram črne škatle preprosto prikazuje vhode in izhode, ki jih naš sistem potrebuje za dokončanje vseh potrebnih procesov. Trudili smo se, da bi bila naša zasnova čim bolj preprosta in osnovna. Naši trije sistemski vhodi so vključevali vodilo senzorjev gibanja (4 za naš pomanjšani model), gumb za preglasitev pešcev in vhod za uro. Na drugi strani je naš edini izhod vodnik LED luči, ki predstavlja naše ulične luči. Za ta model smo uporabili scenarij 16 uličnih luči preprosto zato, ker je to največje število vgrajenih LED izhodov na plošči Basys 3. Nazadnje smo s tem diagramom lahko ustvarili naš projekt Vivado, datoteke vira in omejitve z ustreznimi vhodi in izhodi.

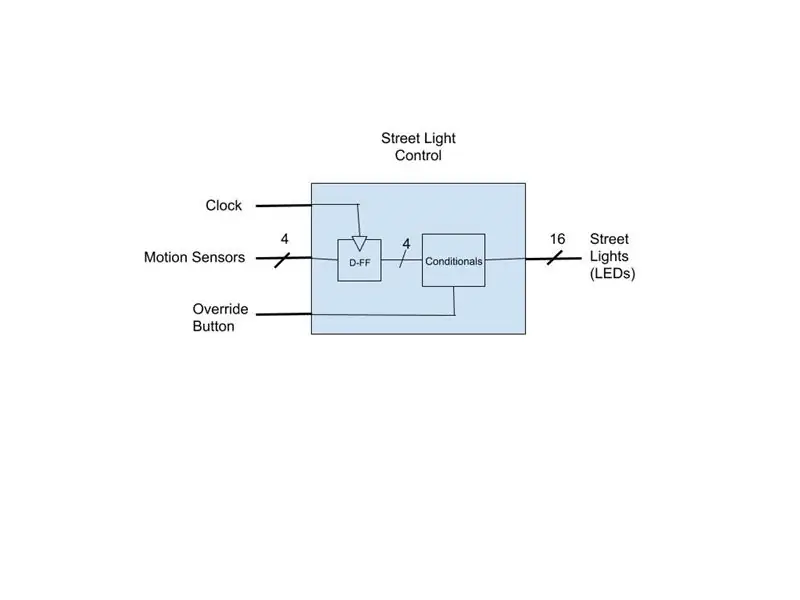

Korak: Komponente

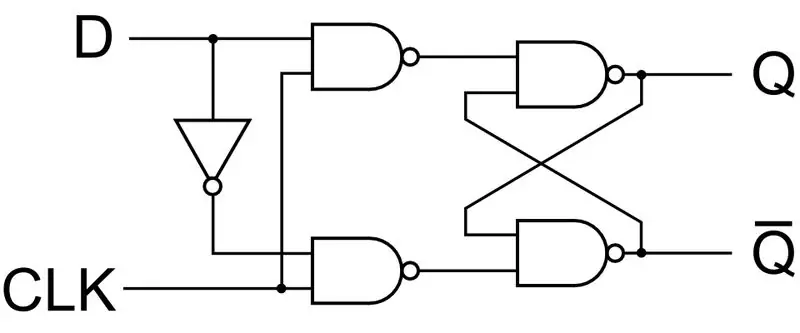

V tem koraku se poglobimo v preučevanje komponent, ki sestavljajo naš diagram črne škatle. Naša prva komponenta je izvorna datoteka VHDL, ki vsebuje D japonke. D japonke preprosto sprejmejo kakršen koli signal, ki se jim vnaša od senzorjev na naraščajočem robu ure, in te podatke zaskoči do naslednjega naraščajočega roba. Tako naši občutljivi senzorji gibanja preprečujejo, da bi izhodne LED "utripale". Prav tako smo na vhodni signal gumba namestili en d-flip-flop, da sveti LED približno 5-7 sekund po pritisku gumba. To smo speljali tudi skozi razdelilnik ure.

entiteta clk_div2 je Port (clk: v std_logic; sclk: out std_logic); konec clk_div2;

arhitektura my_clk_div ali clk_div2 je

konstanta max_count: celo število: = (300000000); signal tmp_clk: std_logic: = '0'; začni my_div: spremenljivka process (clk, tmp_clk) div_cnt: integer: = 0; začni if ((vzpenjajoč se rob (clk)) potem if ((div_cnt = MAX_COUNT) potem tmp_clk <= ne tmp_clk; div_cnt: = 0; else div_cnt: = div_cnt + 1; konec če; konec če; sclk <= tmp_clk; končaj proces my_div; konec my_clk_div;

Naša zadnja komponenta v tem diagramu je vedenjska izvorna datoteka VHDL, ki vsebuje pogoje za izhode, ki temeljijo na konfiguraciji vhodnih signalov.

3. korak: D Natikači

Štiri japonke, priključene na vhodne signale, so bistvene za delovanje našega sistema. Kot smo že povedali, z občutljivimi senzorji gibanja in gumbom za preglas japonke uporabljajo zapahe za oddajanje samo vhodnega signala na naraščajočem robu ure. Ta zaporedna logika pomeni, da lahko naše ulične luči ostanejo prižgane določen čas, potem ko jih sproži hitro gibanje. Kodiranje D-flip flopa je precej preprosto:

beginprocess (CLK) start, če se vzpenjajoči rob (CLK) potem Q <= D; konec če; zaključni postopek;

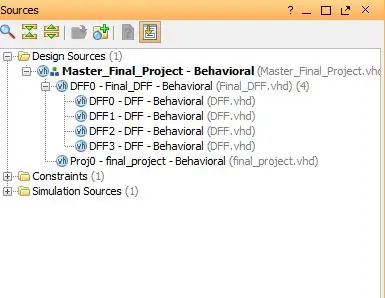

Vse skupaj je mogoče zbrati v eno samo izjavo if. Ko smo imeli ta kos, smo ustvarili strukturno izvorno datoteko VHDL, ki vsebuje vse štiri naše potrebne japonke:

začni DFF0: zemljevid vrat DFF (CLK => CLK, D => D (0), Q => Q (0)); DFF1: zemljevid vrat DFF (CLK => CLK, D => D (1), Q => Q (1)); DFF2: zemljevid vrat DFF (CLK => CLK, D => D (2), Q => Q (2)); DFF3: zemljevid vrat DFF (CLK => CLK, D => D (3), Q => Q (3));

konec vedenjskega;

To pomaga ohraniti našo glavno strukturno datoteko, kjer vse sistemske komponente združimo veliko bolj čiste in organizirane.

4. korak: Pogoji

Da bi bila naša koda kompaktna in učinkovita, smo vse pogoje zapisali v en sam stavek. Za naš pomanjšani model smo imeli 16 možnih LED izhodnih konfiguracij, saj je vsak senzor gibanja odgovoren za skupino 4 LED.:

primer NMS je, ko je "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; zaključni primer;

5. korak: Omejitve

Če želite z Vivadom pravilno navesti svoje vnose in izhode, morate implementirati datoteko z omejitvami, ki navaja vsa uporabljena vrata, gumbe, LED in ure.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [1]} PACK U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACKAGE_PIN W18 get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_PIN U14 [get LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 [get_ports {LED 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] IO set_property STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]}] set_property IOS33 [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTANDARD LVCMOS33 {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33 [get_ports [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [1] PAGE] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

6. korak: Glavna izvorna datoteka

V tej glavni datoteki združujemo vse prej omenjene izvorne datoteke komponent. Ta datoteka deluje kot strukturna koda, ki združuje različne komponente.

entiteta Master_Final_Project je vrata (BTN: v STD_LOGIC; CLK: v STD_LOGIC; MS: v STD_LOGIC_VECTOR (3 navzdol 0); LED: ven STD_LOGIC_VECTOR (15 navzdol 0)); konec Master_Final_Project;

arhitektura Vedenje Master_Final_Project je

komponenta final_project je vrata (--CLK: v STD_LOGIC; NMS: v STD_LOGIC_VECTOR (3 navzdol 0); BTN: v STD_LOGIC; --sw: v STD_LOGIC_Vector (1 navzdol 0); LED: ven STD_LOGIC_VECTOR (15 navzdol 0); končna komponenta;

komponenta Final_DFF je

Vrata (CLK: v STD_LOGIC; D: v STD_LOGIC_Vector (3 navzdol 0); Q: ven STD_LOGIC_Vector (3 navzdol 0)); končna komponenta;

signal DFF02proj30: STD_LOGIC;

signal DFF12proj74: STD_LOGIC; signal DFF22proj118: STD_LOGIC; signal DFF32proj1512: STD_LOGIC;

začeti

DFF0: Končni zemljevid vrat_DFF (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: zemljevid vrat final_project (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); konec vedenjskega;

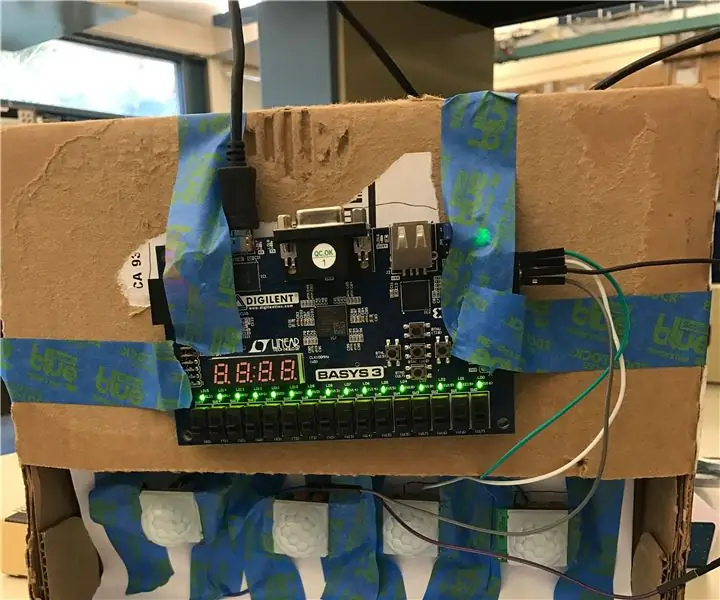

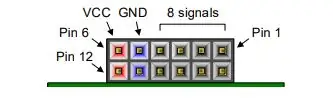

7. korak: Montaža

Sestava strojne opreme za ta projekt je minimalna. Edini potrebni kosi so naslednji:

1. deska Basys 3 (1)

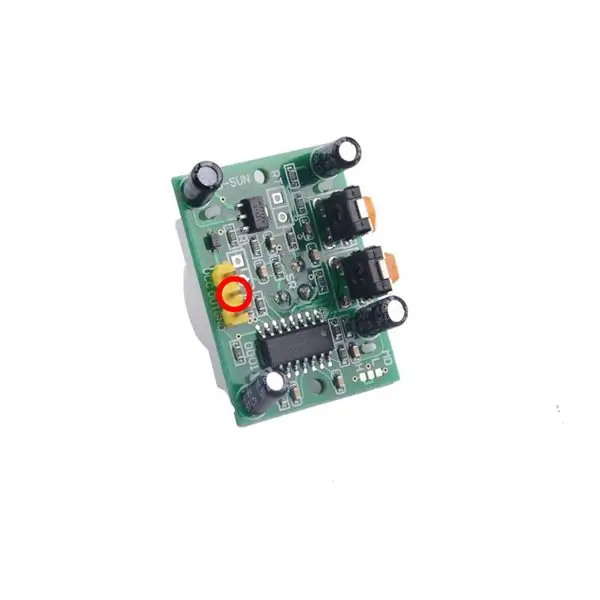

2. Poceni senzorji gibanja, ki jih najdete na Amazonu tukaj. (4)

3. Od moških do žensk (4)

Montaža:

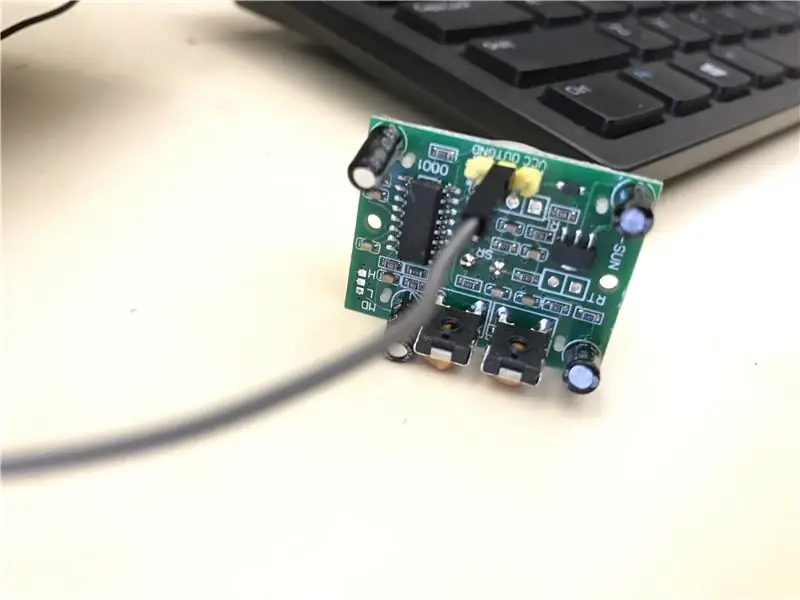

1. Priključite 4 moške kable v vrata JB 1-4 glave PMod (glejte sliko).

2. Priključite ženske konce na izhod vsakega senzorja gibanja.

8. korak: Nalaganje programa

Zdaj smo pripravljeni, da naložimo glavno izvorno datoteko VHDL na ploščo Basys 3. Zagotovite sintezo, implementacijo in generiranje preverjanja bitnih tokov za morebitne napake. Če se vse uspešno zažene, odprite upravitelja strojne opreme in programirajte napravo Basys 3. Vaš projekt je zdaj končan!

Priporočena:

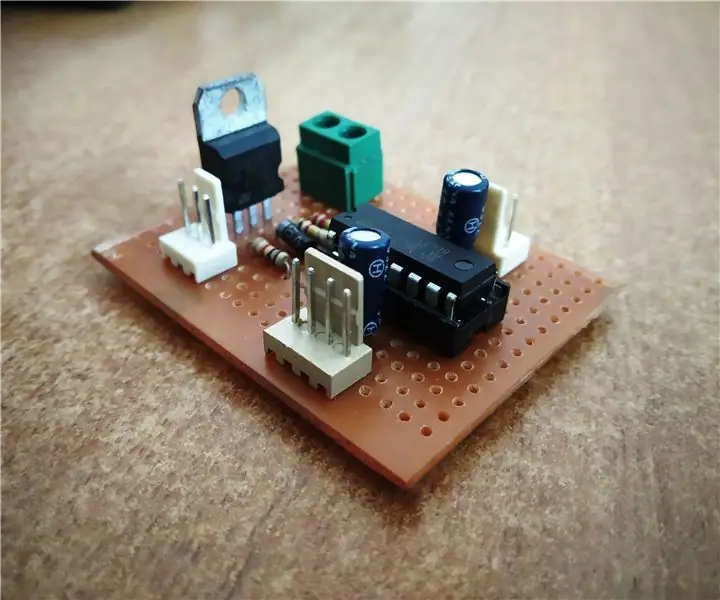

Energetsko učinkovita plošča gonilnika motorja: 5 korakov

Energetsko učinkovita gonilna plošča motorja: Predstavljeni projekt je koračni motor/vezje gonilnika motorja z IC gonilnikom motorja SN754410, vključno z nekaterimi funkcijami varčevanja z energijo. Plošča lahko poganja 2 enosmerna motorja ali koračni motor s pomočjo dvojnega vezja H v IC. SN754410 IC

Nadgradnja stare svetilke / svetilke: 5 korakov (s slikami)

Nadgradnja stare svetilke / svetilke:-= Ideja = -Ta stara svetilka Uniross uporablja eno samo svinčeno-kislinsko baterijo 4 V. Zakaj je ne zamenjate z Li-Ion baterijo, ima podobno napetost. Je manjša, lažja in ima večjo zmogljivost. Gorilnik ima 3 načine: - izmenično preklapljanje med - 20 LED

Učinkovite opombe PDF v Linuxu: 4 koraki

Učinkovite opombe PDF v Linuxu: Ste kdaj potrebovali označevanje dokumentov PDF v Linuxu? Ne govorim o ustvarjanju datotek PDF, kar je mogoče storiti s številnimi orodji, vključno z latex+dvipdf, pdflatex, LibreOffice ali drugimi. Govorim o dodajanju lastnih pripisov poleg obstoja

Nadgradnja LED svetilke iz karbidne svetilke za Rinoa Super-Genius: 5 korakov (s slikami)

Nadgradnja LED svetilke iz karbidne svetilke za Rinoa Super-Genius: Danes na Made To Hack sem dodatno opremil karbidno svetilko! To počnem za kolega YouTuberja Rinoa Super-Genius, da se svetilka lahko uporabi pri projektu električnega kolesa

Kako narediti zvočni sistem nakupovalnega vozička za ulične zabave: 10 korakov

Kako narediti zvočni sistem nakupovalnega vozička za ulične zabave: Ta navodila vam bodo pokazala korake za ustvarjanje samostojnega mobilnega zvočnega sistema v nakupovalnem vozičku. Ta nastavitev se lahko uporablja za vse vrste javnih zborovanj, vključno s protesti, uličnimi plesnimi zabavami, rafalnimi parki Parkling Lot in celo za