Kazalo:

- 1. korak: Konfigurirajte Zynq programabilno logiko za oddajnik

- 2. korak: Konfigurirajte Zynq programabilno logiko za sprejemnik

- 3. korak: Namestite gonilnik VDMA

- 4. korak: Namestite omrežje Nanorouter

- 5. korak: Namestite Zynq Processing System za prenos podatkov prek etherneta

- Korak 6: Nastavite Zynq Processing System za sprejem podatkov prek Etherneta

- Korak 7: Priključite plošče Zybo na vir HDMI in umivalnik HDMI

- 8. korak: Alternativne ideje za izboljšanje

- 9. korak: Dostopnost

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:05.

- Nazadnje spremenjeno 2025-01-23 15:09.

Ste si kdaj želeli, da bi televizor lahko priključili na računalnik ali prenosni računalnik kot zunanji monitor, pa niste želeli imeti na poti vseh teh nadležnih kablov? Če je tako, je ta vadnica samo za vas! Čeprav obstaja nekaj izdelkov, ki dosegajo ta cilj, je projekt DIY veliko bolj zadovoljiv in potencialno cenejši.

Ta koncept se razlikuje od izdelkov, kot je chromecast, saj naj bi namesto kabla HDMI, ki se poveže z monitorjem, namesto kot pretočna naprava.

Naš projekt je nastal kot končni projekt za tečaj operacijskih sistemov v realnem času na Kalifornijski državni politehnični univerzi v San Luis Obispu.

Cilj projekta je uporabiti dve plošči Digilent Zybo kot brezžični komunikacijski vmesnik med oddajno napravo HDMI (računalnik, blu-ray itd.) Do sprejemne naprave HDMI (namizni monitor, projektor, televizija itd.).

En Digilent Zybo bo prek HDMI povezan z oddajno napravo, drugi pa prek HDMI prek sprejemne naprave.

Brezžična komunikacija bo vzpostavljena z uporabo brezžičnega lokalnega omrežja, namenjenega oddajniku in sprejemniku, ne da bi bila usmerjena skozi domači usmerjevalnik ali drugo takšno napravo. Brezžični modul, uporabljen za ta projekt, je nano usmerjevalnik tplink wr802n, od katerih eden deluje kot dostopna točka za vzpostavitev omrežja, drugi pa kot odjemalec za povezavo z omrežjem. Vsak nano usmerjevalnik bo povezan prek ethernetnega kabla na katero koli ploščo Zybo. Ko so povezane s temi usmerjevalniki, bodo naprave komunicirale prek TCP, kot da bi bile povezane z enim ethernetnim kablom (kar pomeni, da je za vzpostavitev povezave potrebna le konfiguracija IP -naslov odjemalca).

Čeprav je bil cilj projekta olajšati pretok videa 1080x720 pri 60 Hz, to zaradi omejitev pasovne širine v brezžičnem omrežju in pomanjkanja stiskanja videa v realnem času za zmanjšanje podatkov, potrebnih za pošiljanje, ni bilo dosegljivo. Namesto tega ta projekt služi kot okvir za prihodnji razvoj za dosego tega cilja, saj je močno omejil omejitve hitrosti sličic za pravilno pretakanje podatkov HDMI, kot je bilo predvideno.

Zahteve za projekt:

2x Digilent Zybo razvojne plošče (imeti morajo vsaj en priključek HDMI)

2x HDMI kabla

2x microusb kabla (za povezavo Zybo z osebnim računalnikom za razvoj)

2x nano usmerjevalniki tplink wr802n (vključno z dodatnimi 2x adapterji za mikro USB in stensko vtičnico)

2x ethernet kabel

*** Opomba: Ta vadnica predpostavlja poznavanje paketa Vivado design in izkušnje pri ustvarjanju novega projekta in oblikovanja blokov. ***

1. korak: Konfigurirajte Zynq programabilno logiko za oddajnik

Naš pristop k razvoju programabilne logike oddajnika je bil izvajanje prehoda hdmi-to-hdmi iz računalnika na monitor z uporabo dveh blokov za video Direct Direct Memory Access (VDMA), enega za pisanje in enega za branje.

Oba sta izbrana za prosto delujoč način 3 medpomnilnika okvirjev (0-1-2). Ker je video jedro optimizirano za 60 sličic na sekundo, to pomeni, da bo VDMA zapisoval ali bral v nov okvir vsakih 16,67 ms v tem vrstnem redu: 0, 1, 2, 0, 1, 2, 0, 1, 2. Lokacije pomnilnika DDR za vsak okvir so različne za oba VDMA, ker nista več sinhronizirana med seboj. Namesto tega se za sinhronizacijo gibanja podatkov med dvema pomnilniškima mestoma uporablja strojni časovnik (TTC1), konfiguriran za 60 Hz.

Na zgornji sliki so prikazani 3 okvirji, njihove dimenzije in količina pomnilnika (na desni strani okvirja). Če tem pomnilniškim mestom dodelimo zapisovalni VDMA, potem lahko dodeljene pomnilniške pomnilniške lokacije VDMA dodelimo izven tega niza, recimo začenši z 0x0B000000. Vsak okvir je sestavljen iz 1280*720 slikovnih pik, vsaka slikovna pika pa je sestavljena iz 8 bitov rdeče, zelene in modre barve za skupno 24 bitov. To pomeni, da je okvir sestavljen iz 1280*720*3 bajtov (2,76 MB).

Znotraj časovnika IRQ, ki je opisan v nastavitvi gonilnika VDMA, bo obravnaval kopiranje podatkov med dvema pomnilniškima mestoma VMDA. VDMA ponuja kazalec na trenutni okvir, iz katerega se piše ali bere. Okvir predstavlja posebna siva koda, ki se pretvori v programsko opremo. Definicije sive kode za konfiguracijo vmesnega vmesnika s tremi okvirji najdete v priročniku za izdelke AXI VDMA v dodatku C.

To nam omogoča kopiranje zapisane vsebine v pomnilnik brez branja iz okvirja, v katerega se trenutno piše.

*** Upoštevajte, da se prebrani VDMA ne uporablja pri pošiljanju podatkov po brezžičnem omrežju. Njegov edini namen je preveriti pravilno delovanje kopiranja pomnilnika iz zapisovalnega VMDA. Branje VMDA je treba onemogočiti. ***

Tu so koraki za ustvarjanje bloka za oblikovanje oddajnika:

- Pri ustvarjanju novega projekta je dobro, da projektu dodelite čip ali ploščo. Na tej povezavi je opisano, kako v imenik Vivado dodate nove datoteke plošč in ustrezno ploščo povežete s svojim projektom. To bo še kako prav pri dodajanju bloka Processing System in prehodu s strojne na programsko opremo (stran SDK).

-

Dodajte naslednje bloke:

- dvi2rgb

- Video v Axi4-stream

- Krmilnik časa

- axi4-stream za vid ven

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Čarovnik za uro

- Konstantno

- Zynq procesni sistem

- Ko dodajate sistem za obdelavo, kliknite "Zaženi samodejno blokiranje" v zgornji zeleno obarvani vrstici in se prepričajte, da je izbrana možnost "Uporabi prednastavitev plošče". Vse ostalo pustite privzeto.

- Slike vsakega okna za konfiguracijo bloka najdete na zgornjih slikah. Če za določeno okno ne vidite slike, jo pustite privzeto.

-

Začnite konfigurirati sistem obdelave Zynq:

- V konfiguraciji PS-PL AXI Non Secure Omogoči GP Master AXI, omogoči vmesnik M AXI GP0

- V konfiguraciji PS-PL Slave AXI Interface vklopite HP0 in HP1

- V konfiguraciji MIO preverite, ali je ENET0 omogočeno pod V/I perifernimi napravami, nato enota procesorja aplikacij, omogočite Timer0

- V konfiguraciji ure PL Fabric Clocks omogočite FCLK_CLK0 in nastavite na 100 MHz.

- Kliknite V redu

- Preden kliknete »Zaženi samodejno povezovanje«, povežite video bloke, kot je prikazano na zgornji sliki zasnove bloka TX. Konstanto boste želeli preimenovati v VDD in vrednost nastaviti na 1. Video bloke ustrezno povežite.

- Ura HDMI TMDS in podatkovni zatiči HDMI bodo zunanji na blokih rgb2dvi in dvi2rgb

- Ustvarite vhodna in izhodna vrata za signal zaznavanja vročih vtičev (HPD) in jih povežite skupaj, to je definirano v datoteki omejitev

-

Ura slikovnih pik je obnovljena iz TMDS_Clk_p, ki je ustvarjena v datoteki omejitev. To bo 74,25 MHz v skladu z ločljivostjo 720p. Pomembno je, da uro pikslov (iz bloka dvi2rgb) povežete z naslednjimi zatiči:

- vid_io_in_clk (vid v blok axi toka)

- vid_io_out_clk (axi tok v vid izhodni blok)

- clk (krmilnik časa)

- PixelClk (rgb2dvi)

- *** Opomba: Če želite aktivirati obnovitev ure slikovnih pik, morate priključka HDMI rx in tx priključiti na aktivni vir/umivalnik. Eden od načinov za to je ločitev video rx in tx blokov na različne domene ure (z drugimi besedami, ustvarite novo uro 74,25 MHz za vnos v blok tx). ***

- Nato nastavite čarovnika za uro, tako da imate 100 MHz vhod (globalni vmesni vir) in 3 izhodne ure pri 50 MHz (ura AXI-Lite), 150 MHz (ura AXI4-Stream), 200 MHz (dvi2rgb RefClk pin).

- Priključite pin računalniškega sistema FCLK_CLK0 na vhod čarovnika za uro

- Na tej točki kliknite "Zaženi samodejno povezovanje" v zeleni vrstici na vrhu okna za načrtovanje. To je dobro narediti za en blok naenkrat in slediti zgornji sliki zasnove bloka TX.

- Orodje bo poskušalo dodati povezavo AXI Interconnect, ki deluje kot povezovalna enota master/slave za bloke, ki uporabljajo vodilo AXI-Lite (VDMA in GPIO).

- Dodala bo tudi AXI SmartConnect, ki deluje kot povezovalna enota master/slave za vmesnike AXI4-Stream in visoko zmogljive procesorje, ki jih uporablja VDMA (Stream to Memory Map in obratno).

- Orodje bo dodalo tudi ponastavitev procesorskega sistema. Prepričajte se, da je to povezano samo z VDMA, GPIO in bloki, povezanimi s procesorjem. Ne povezujte ga z nobenim video blokom (npr. Dvi2rgb, krmilnikom časa, videom za tok itd.)

- Ko je avtomatizacija povezave končana, preverite, ali se povezave ujemajo s tistimi na sliki zasnove bloka TX. Opazili boste dodaten blok sistemske ILA, ki ni omenjen. To je samo za odpravljanje napak in zaenkrat ni potrebno. Uporablja ponastavitev procesorja 150M, zato tudi to ni potrebno. Kjer koli vidite majhne zelene "hrošče" na avtobusih, to je zaradi mednarodne mednarodne pomoči in jih je mogoče prezreti.

- Zadnji korak je, da z desno miškino tipko kliknete zasnovo bloka v drevesu virov projekta in izberete "Ustvari ovoj HDL." Če nameravate v ovoj dodati logiko, se bo vsakič, ko to izberete, prepisala.

- Za podrobnosti o strani SDK glejte razdelek VDMA Driver Setup.

Ure in ponastavitve

Ugotovil sem, da je najpomembnejši vidik vsakega programabilnega logičnega projekta natančno upoštevanje domen ure in signalov za ponastavitev. Če so te pravilno konfigurirane, imate dober uspeh pri oblikovanju.

Ura Pixel in čas zaklenjeni

Za preverjanje, ali so nekateri signali aktivni, je dobro, da te signale povežete z LED diodami (ure, ponastavitve, ključavnice itd.). Dva signala, za katera se mi je zdelo koristno slediti na oddajniški plošči, sta ura slikovnih pik in signal "zaklenjen" na bloku AXI4-Stream to video out, ki vam pove, da je bil čas video sinhroniziran s krmilnikom časovnika in video virom. podatkov. Ovojniku oblikovalskega bloka sem dodal nekaj logike, ki spremlja uro pikslov z uporabo signala PixelClkLocked na bloku dvi2rgb kot ponastavitev. Tukaj sem priložil datoteko kot hdmi_wrapper.v. Tukaj je priložena tudi datoteka omejitev.

2. korak: Konfigurirajte Zynq programabilno logiko za sprejemnik

Programabilni logični blok za sprejemnik je enostavnejši. Ključna razlika, razen manjkajočih vhodnih blokov hdmi, je odsotnost obnovljene ure slikovnih pik. Zato moramo iz čarovnika za uro ustvariti lastnega. To zasnovo je treba narediti v ločenem projektu od oddajnika. Za naše namene je projekt sprejemnika sledil plošči Zybo 7Z-20, oddajnik pa plošči Z7-10. FPGA -ji na ploščah so različni, zato … bodite previdni.

Tu so koraki za ustvarjanje bloka za oblikovanje sprejemnika:

-

V svojo zasnovo dodajte naslednje bloke ip:

- Krmilnik časa

- AXI4-tok za video izhod

- RGB v DVI

- AXI VDMA

- AXI GPIO

- Procesni sistem

- Čarovnik za uro

- Konstantno (VDD nastavljeno na 1)

- Za konfiguracijo teh blokov sledite istemu vzorcu kot oddajnik. Tu so vključene slike za opazne razlike v konfiguraciji. Drugi ostanejo enaki oddajniku.

- VDMA za to zasnovo konfigurirajte samo kot kanal za branje. Onemogočite kanal za pisanje.

-

Čarovnika za uro je treba konfigurirati za naslednje izhode:

- clk_out1: 75 MHz (ura slikovnih pik)

- clk_out2: 150 MHz (tok)

- clk_out3: 50 MHz (axi-lite ura)

- Povežite video bloke, kot je prikazano na sliki oblikovanja bloka RX.

- Nato zaženite avtomatizacijo povezave, ki bo dodala bloke AXI Interconnect, AXI SmartConnect in System Reset in poskušala vzpostaviti ustrezne povezave. Pojdite počasi sem in se prepričajte, da ne izvaja neželenih povezav.

- Ura HDMI TMDS in podatkovni zatiči naj bodo zunanji na bloku rgb2dvi

- Pri tej zasnovi ni potrebe po signalu vročega vtiča.

3. korak: Namestite gonilnik VDMA

Nastavitev za različne bloke, ki so konfigurirani prek vmesnika AXI-Lite, je najbolje narediti z uporabo demo projektov, vključenih v BSP kot referenco. Po izvozu strojne opreme za oblikovanje in zagonu SDK -ja iz Vivada boste želeli dodati nov paket podpore za ploščo in v okno z nastavitvami BSP vključiti knjižnico lwip202. Odprite datoteko system.mss iz BSP in videli boste zunanje gonilnike, ki so prisotni v zasnovi vašega bloka. Možnost "Primeri uvoza" vam omogoča uvoz uvoženih demo projektov, ki uporabljajo te zunanje naprave, in vam tako pokaže, kako jih konfigurirati v programski opremi z razpoložljivimi gonilniki Xilinx (glejte sliko v prilogi).

To je bila metoda, uporabljena za konfiguracijo VDMA, Timer & Interrupt in GPIO. Tu je vključena izvorna koda za prenos in sprejem. Razlike so skoraj izključno v main.c.

*** OPOMBA: Ker sistem v času pisanja te vadnice ni v celoti deloval, izvorna koda v tem razdelku ne vključuje kode brezžičnega omrežja. Zaradi združevanja projektov za prenos/sprejem video jedra z projekti za prenos/sprejem v omrežju je treba odpraviti več napak. Zato jih ta vadnica zaenkrat obravnava ločeno. ***

Funkcija vodnika prekinitev TX (IRQHandler)

Ta funkcija bere sive kode, ki jih zagotavljajo branje in pisanje VDMA preko blokov GPIO. Sive kode se pretvorijo v decimalno in se uporabijo za izbiro osnovne lokacije pomnilnika okvirja trenutnega okvirja. Kopiran okvir je prejšnji okvir od tistega, ki ga zapisuje VDMA (npr. Če VDMA piše v okvir 2, kopiramo okvir 1; če piše v okvir 0, zavijemo in preberemo iz okvira 2).

Funkcija zajema le vsak 6. okvir, da zmanjša hitrost sličic na 10 Hz in ne na 60 Hz. Zgornja meja omrežja je 300 Mbps. Pri 10 sličicah na sekundo je potrebna pasovna širina 221,2 Mbps.

Komentiranje/odstranjevanje komentarjev dveh vrstic v tej funkciji bo uporabniku omogočilo prehod v način passthru HDMI za namene odpravljanja napak/preizkusa (koda je komentirana tako, da označuje ustrezne vrstice). Trenutno kopira okvir na pomnilniško mesto, ki ga uporablja koda ethernet.

Funkcija upravljalnika prekinitev RX (IRQHandler)

Ta funkcija je zelo podobna funkciji TX, vendar kopira iz 2 medpomnilnika FIFO, ki ga ethernet uporablja za pisanje dohodnih podatkov. Koda ethernet označuje, v kateri okvir se zapisuje FIFO, podatki se kopirajo iz nasprotnega okvira. Podatki se kopirajo v okvir neposredno za tistim, ki ga bere VDMA, da se prepreči trganje.

4. korak: Namestite omrežje Nanorouter

Če želite ustvariti omrežje z nano usmerjevalniki TPlink, jih vklopite posamično in se povežite s privzetim SSID -jem WiFi za naprave. Več informacij o konfiguracijskih nastavitvah za to posebno napravo najdete v uporabniškem priročniku naprave.

Nastavite eno od naprav kot dostopno točko, ta bo delovala kot primarna povezava za omrežje. Ne pozabite poimenovati omrežje in si zabeležiti ime ter onemogočiti DHCP (ne želimo, da usmerjevalnik dinamično konfigurira naslove IP, želimo, da plošče oddajnika in sprejemnika Zybo same nastavijo svoje naslove IP, da bodo skladne). Po konfiguraciji se prepričajte, da se naprava znova zažene in vzpostavi to omrežje.

Drugo napravo nastavite kot odjemalca in se prepričajte, da je povezana z omrežnim SSID -om, ki ste ga nastavili s prvim nano usmerjevalnikom. Še enkrat se prepričajte, da je DHCP za odjemalca onemogočen.

Ko je odjemalec končan in znova zagnan, se mora povezati z nano usmerjevalnikom dostopne točke (v nasprotnem primeru obstaja verjetno težava v konfiguraciji ene od naprav). Opazili boste, da bo LED lučka na odjemalcu neprekinjeno, ko se poveže z dostopno točko.

LED nano usmerjevalnika dostopne točke bo na tej točki verjetno še naprej utripala, to je v redu! Utripajoča lučka pomeni, da ni priključena na drugo napravo prek ethernetnih vrat, in ko je povezana z konfiguriranim Zybo, bo LED svetila neprekinjeno, kar kaže na uspešno omrežno povezavo.

Zdaj, ko imamo nastavljene nano usmerjevalnike, imamo brezžično omrežje, ki nam bo omogočalo komunikacijo. Pomembno opozorilo je, da nam naša konfiguracijska metoda za nano usmerjevalnike (kot dostopno točko in odjemalca) omogoča komunikacijo z oddajne plošče Zybo na sprejemno ploščo Zybo, kot da sta oba povezana z eno samo ethernetno žico. Zaradi tega je naša omrežna nastavitev manj težka, saj bi alternativa verjetno vključevala konfiguracijo plošč Zybo za izrecno povezavo s strežnikom skupaj z predvideno povezavo.

Ko sta obe napravi nastavljeni, so nano usmerjevalniki konfigurirani in pripravljeni za uporabo v vašem omrežju WIDI. Med nano -usmerjevalniki in ploščami Zybo ni posebnega seznanjanja, saj bosta dostopna točka ali odjemalec delovali bodisi za oddajno ali sprejemno napravo.

5. korak: Namestite Zynq Processing System za prenos podatkov prek etherneta

Za prenos podatkov HDMI z ene plošče Zybo na drugo moramo v naš gonilnik VDMA vključiti protokol Ethernet. Naš cilj je pretakanje posameznih video okvirjev prek zunanje enote Ethernet v procesorskem sistemu z nastavljeno hitrostjo, ki je skladna z našo pasovno širino omrežja. Za naš projekt smo uporabili TCP, ki ga zagotavlja goli kovinski API LwIP. Ker sta oba člana projekta relativno neizkušena s pripomočki za mreženje, je bila ta izbira sprejeta, ne da bi se popolnoma zavedali posledic in omejitev, povezanih s TCP. Največji problem pri tej izvedbi je bila omejena pasovna širina in dejstvo, da res ni zasnovana za prenos velike količine podatkov. Nadaljnje rešitve za zamenjavo TCP in izboljšanje tega projekta bodo obravnavane kasneje.

Kratek opis TCP z LwIP: Podatki se pošiljajo po omrežju v paketih velikosti tcp_mss (največja velikost segmenta TCP), ki je običajno 1460 bajtov. Klic tcp_write bo vzel nekaj podatkov, na katere se nanaša kazalec, in konfiguriral pbufs (paketni vmesni pomnilnik) za shranjevanje podatkov in zagotavljanje strukture za operacije TCP. Največja količina podatkov, ki jih je mogoče naenkrat postaviti v čakalno vrsto, je nastavljena kot tcp_snd_buf (vmesni prostor pošiljatelja TCP). Ker je ta parameter 16 -bitno število, smo omejeni na velikost medpomnilnika za pošiljanje 59695 bajtov (v vmesnem pomnilniku za pošiljanje je potrebno nekaj oblazinjenja). Ko so podatki v čakalni vrsti, se pokliče tcp_output za začetek prenosa podatkov. Pred pošiljanjem naslednjega segmenta podatkov je nujno, da so bili vsi prejšnji paketi uspešno poslani. Ta postopek se izvede s funkcijo recv_callback, saj je to funkcija, ki se pokliče, ko je potrditev vidna s sprejemnika.

Uporaba primerov projektov v Vivado SDK je v veliko pomoč pri spoznavanju delovanja LwIP TCP in je dobro izhodišče za začetek novega projekta.

Postopek za oddajno napravo WiDi je naslednji:

- Inicializirajte omrežje TCP s klici funkcije gonilnika gole kovine LWIP.

- Določite vse funkcije povratnega klica, potrebne za omrežne operacije.

- Povežite se s sprejemnikom WiDi tako, da se povežete z njegovim naslovom IP in vrati (naša konfiguracija: IP sprejemnika je 192.168.0.9, povežite se z vrati 7).

- Ko časovnik za gonilnik VDMA poteče, vnesite TX ISR.

- Določite trenutni medpomnilnik okvirja za dostop na podlagi sive kode VDMA

- Prvi segment podatkov v medpomnilniku za pošiljanje TCP postavite v čakalno vrsto

- Iznesite podatke in posodobite lokalne spremenljivke, da spremljate, koliko podatkov je bilo poslanih za trenutni okvir.

- Ko dosežete prejeti povratni klic (klic funkcije, opravljen po tem, ko oddajnik prejme potrditev pridobivanja podatkov), postavite naslednji del podatkov v vrsto.

- Ponovite koraka 7 in 8, dokler ni poslan celoten okvir.

- Vrnite se v stanje mirovanja, da počakate na naslednjo prekinitev časovnika, da označite, da je nov okvir pripravljen (Nazaj na korak 4).

Nastavite nastavitve LwIP paketa za podporo, kot je prikazano na zgornji sliki. Vse vrednosti so privzete, razen za tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Upoštevajte tudi, da je podrobno odpravljanje napak mogoče doseči s spreminjanjem parametrov BSP za skupino debug_options.

Korak 6: Nastavite Zynq Processing System za sprejem podatkov prek Etherneta

Razvojna plošča Zybo, ki bo delovala kot brezžični sprejemnik, bo delovala podobno kot oddajna naprava. Nastavitve paketa za podporo plošč za LwIP bodo enake tistim v prejšnjem koraku.

Naprava bo prevzela pakete, ki vsebujejo segmente video okvirja, iz nano usmerjevalnika in bo kopirala podatke video okvirja v medpomnilniški prostor s tremi okvirji za sprejemni VDMA. Da bi se izognili prepisovanju podatkov, se pri zbiranju podatkov iz nanosilnika uporablja dvojni podatkovni vmesni pomnilnik (imenovali ga bomo omrežni vmesni pomnilnik), tako da se lahko omrežni promet nadaljuje, medtem ko se prejšnji celoten video okvir kopira v VDMA vmesnik.

Postopek za sprejemno napravo WiDi zahteva dve nalogi, od katerih ena prejema ethernetne podatke, druga pa je kopiranje video okvirjev iz omrežnega medpomnilnika v vmesnik s tremi sličicami VDMA.

Naloga sprejema Ethernet:

- Inicializirajte omrežje TCP s klici funkcije gonilnika gole kovine LWIP (nastavitev z naslovom IP, s katerim se bo oddajnik povezal, 192.168.0.9 v našem)

- Določite vse funkcije povratnega klica, potrebne za omrežne operacije.

- Ko prejmete paket Ethernet, kopirajte paketne podatke v trenutni omrežni vmesnik, povečajte trenutno nakopičene podatke.

- Če paket zapolni omrežni vmesni okvir, nadaljujte s korakoma 5 in 6. V nasprotnem primeru se vrnite na korak 3 za to nalogo.

- signal, da mora naloga vmesnega vmesnika s tremi okvirji VDMA kopirati iz na novo dokončanega omrežnega vmesnika.

- Preklopite na drug omrežni vmesnik in nadaljujte z zbiranjem podatkov prek etherneta.

- Neaktiven, dokler ne prejmete novega ethernetnega paketa (korak 3).

Kopirajte omrežni vmesnik v vmesnik VDMA s tremi okvirji:

- Ko časovnik za gonilnik VDMA poteče, vnesite RX ISR.

- Določite trenutni medpomnilnik okvirja za dostop na podlagi sive kode VDMA.

- Določite, kateri omrežni vmesnik bo kopiran v vmesnik VDMA, in kopirajte te podatke

Korak 7: Priključite plošče Zybo na vir HDMI in umivalnik HDMI

Zdaj priključite kable hdmi za sprejemnik in oddajnik, programirajte FPGA in zaženite procesorski sistem. Hitrost sličic bo verjetno zelo počasna zaradi velikih stroškov delovanja LwIP in omejene pasovne širine. Če obstajajo težave, se povežite prek UART in poskusite prepoznati opozorila ali napake.

8. korak: Alternativne ideje za izboljšanje

Velika težava pri tem projektu je bila količina podatkov, potrebnih za pošiljanje prek WiFi. To je bilo pričakovano, vendar smo podcenjevali vpliv, ki bi ga to imelo, in privedlo do večjega števila slik na zaslonu namesto video vira. Ta projekt lahko izboljšate na več načinov:

- Stiskanje videa v realnem času. Stiskanje dohodnega video vira po kadru bi močno zmanjšalo količino podatkov, ki jih je treba poslati po omrežju. V idealnem primeru bi to storili v strojni opremi (kar ni lahka naloga) ali pa v programski opremi z uporabo drugega jedra ARM za izvajanje algoritmov stiskanja (to bi zahtevalo dodatne analize, da bi zagotovili, da bo čas potekal). V spletu smo našli nekaj odprtokodnih komponent za stiskanje videa v realnem času, vendar je večina IP.

- Izvajanje Ethernet toka v strojni opremi in ne v programski opremi. Zaradi pomanjkanja prostora, ki je na voljo za odlaganje odhodnih podatkov v čakalno vrsto v oddajniku, je bilo zaradi restrikcije velikosti segmenta veliko stroškov. Precej učinkovitejši postopek je uporaba protokola IP AXI Ethernet z vmesnikom FIFO ali DMA za vnos podatkov vanj. To bi zmanjšalo dodatno prtljago iz LwIP TCP in omogočilo večji pretok podatkov.

9. korak: Dostopnost

Rezultat tega projekta WiDi bi moral biti popolnoma integriran, kompakten par naprav, ki bi jih uporabnik lahko priključil na kateri koli vir HDMI in nato brezžično potopil video vir na zaslon s funkcijo HDMI. Naprave bi vsebovale Zynq-7000 SoC, ki ga najdemo na referenčni plošči Zybo, in vključevale omrežno strojno opremo, ki jo najdemo v nano-usmerjevalnikih TP-Link. V idealnem primeru bi lahko uporabnik upravljal oddajni modul z diskretne lokacije v ciljnem operacijskem sistemu, pri čemer bi potreboval le majhne tehnične sposobnosti.

Varnost in povezljivost

Naprave bi morale vključevati tudi varnost transportnega sloja (TLS) in imeti omejeno možnost samodejne povezave, tako zaradi zasebnosti. Namen oblikovalcev je, da povezavo z zaslonom prek brezžičnega vmesnika namenoma naredijo v imenu uporabnika, da se izognejo napačni oddaji občutljivega materiala.

Trenutno stanje

Do tega trenutka je stanje projekta še vedno v teku. Da bi lahko trenutni uporabnik končne točke izkoristil to vadnico, mora imeti dobro tehnično razumevanje zasnove vgrajenega sistema in mora biti seznanjen s programirano strojno opremo in vdelano programsko opremo, ki delujejo skupaj.

Podatki, poslani po omrežju, na tem mestu niso šifrirani in se domneva, da gre za surov prenos paketov TCP/IP.

Projekt video jedra je bil uspešno preizkušen tako za prenos kot za sprejem. Po drugi strani je bila vzpostavljena brezžična povezava med dvema ploščama zybo in podatki o preskusnem okvirju so bili uspešno poslani. Še vedno pa je treba omrežno kodo združiti z vsakim video jedrnim projektom in preizkusiti prenos dejanskih video okvirjev.

Priporočena:

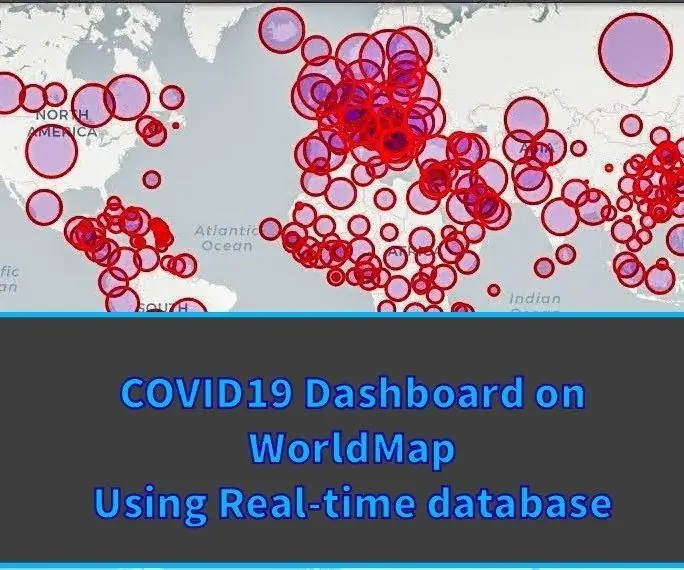

Nadzorna plošča COVID19 na zemljevidu sveta (z uporabo Pythona): 16 korakov

Nadzorna plošča COVID19 na svetovnem zemljevidu (z uporabo Pythona): Vem, da skoraj vsi poznamo večino podatkov o virusu COVID19. To navodilo je namenjeno ustvarjanju zemljevida z mehurčki za risanje podatkov (primerov) v realnem času na zemljevidu sveta. Za več udobja , program sem dodal v skladišče Github: https: //github.co

Quadcopter z uporabo plošče Zybo Zynq-7000: 5 korakov

Quadcopter z uporabo plošče Zybo Zynq-7000: Preden začnemo, si za projekt želite nekaj stvari: Seznam delov1x Digilent Zybo Zynq-7000 plošča 1x okvir Quadcopter, ki lahko namesti Zybo (priložena datoteka Adobe Illustrator za lasersko rezanje) 4x Turnigy D3530/ 14 brezkrtačnih motorjev 1100KV 4x

Orange PI HowTo: Nastavite ga za uporabo s 5 -palčnim HDMI TFT LCD zaslonom: 8 korakov (s slikami)

Orange PI HowTo: Nastavite ga za uporabo s 5 -palčnim HDMI TFT LCD zaslonom: Če ste bili dovolj preudarni, da skupaj s svojim oranžnim PI naročite HDMI TFT LCD zaslon, vas verjetno težave ne poskušajo prisiliti, da deluje . Medtem ko drugi sploh niso mogli opaziti nobenih ovir. Ključno je, da obstajajo le

UDuino: Razvojna plošča, združljiva z Arduinom, zelo poceni: 7 korakov (s slikami)

UDuino: Zelo nizki stroški Arduino združljiva razvojna plošča: Arduino plošče so odlične za izdelavo prototipov. Vendar pa postanejo precej dragi, če imate več sočasnih projektov ali potrebujete veliko krmilnih plošč za večji projekt. Obstaja nekaj odličnih in cenejših alternativ (Boarduino, Freeduino), toda

Razvojna plošča Atmega16/32 z LCD: 8 korakov

Razvojna plošča Atmega16/32 z LCD -jem: Ta navodila vam pokažejo, kako narediti lastno razvojno ploščo za procesorje Atmega16 ali Atmega32. Internet je poln domačih razvojnih plošč, vendar mislim, da je še prostora za drugo. Ta tabla je bila zelo koristna pri mojem projektu