Kazalo:

- Korak: Dodajte vire in izberite »Dodaj ali ustvari vire simulacije«

- Korak: Ustvarite datoteko z imenom Enable_sr_tb

- Korak: Ustvarite datoteko Testbench

- 4. korak: Enable_sr_tb nastavite kot najvišjo raven pod simulacijo

- 5. korak: Zaženite sintezo in vedenjsko simulacijo

- Korak 6: Ocenite rezultat simulacije

- Avtor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:07.

- Nazadnje spremenjeno 2025-01-23 15:09.

Ta simulacijski projekt sem naredil za spletni tečaj. Projekt je napisal Verilog. V Vivadu bomo uporabili simulacijo za vizualizacijo valovne oblike v enable_sr (številka za omogočanje) iz predhodno ustvarjenega projekta štoparice. Poleg tega bomo s sistemsko nalogo prikazali napake, ki smo jih naredili pri načrtovanju.

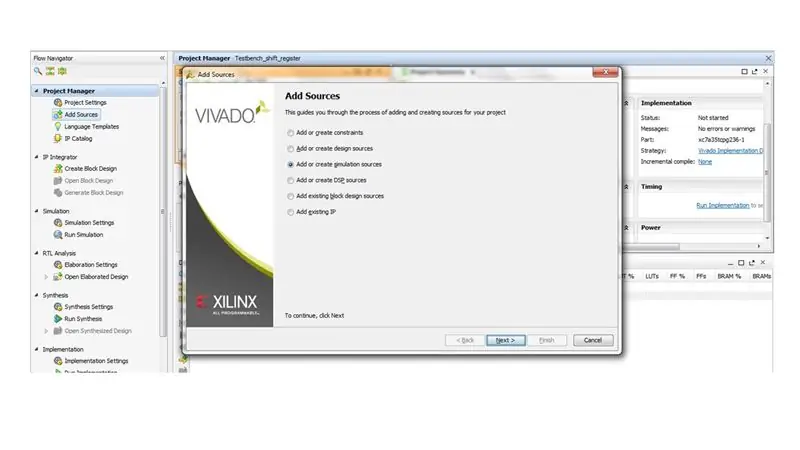

Korak: Dodajte vire in izberite »Dodaj ali ustvari vire simulacije«

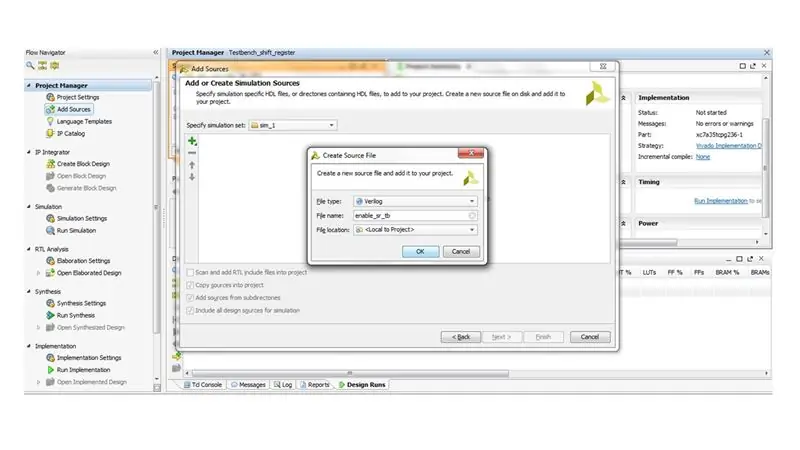

Korak: Ustvarite datoteko z imenom Enable_sr_tb

Korak: Ustvarite datoteko Testbench

1. Uvozi modul enable_sr iz projekta štoparica. To je datoteka, ki jo želimo simulirati

2. Ustvari testbench modul enable_sr_tb ();

3. Vnesite vhode in izhode modula enable_sr (). Ne pozabite, da so vhodi za enable_sr zdaj v registrskem tipu, medtem ko izhodi postanejo neto.

4. Naredite preskusno enoto (uut), ki je enable_sr

5. Ustvarite uro, katere obdobje (T) je 20ns

6. S pogojnim stavkom ustvarite sistem za preverjanje napak. V tem primeru želimo preveriti, ali je aktivnih več kot ena številka.

Opomba: V prvotni datoteki enable_sr () bi morali vzorec zagnati kot 4'b0011, tako da sta dve števki aktivni za ustvarjanje napake

7. Za prikaz napake uporabite sistemsko nalogo $ display

8. S sistemsko nalogo $ finish dokončajte simulacijo v času 400ns

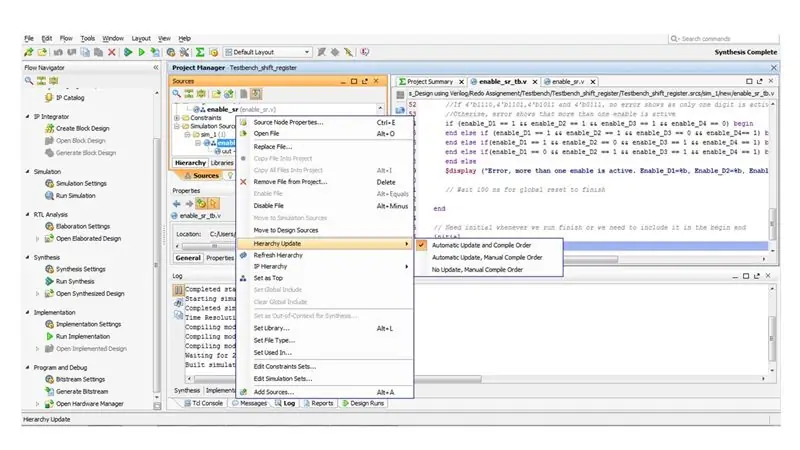

4. korak: Enable_sr_tb nastavite kot najvišjo raven pod simulacijo

5. korak: Zaženite sintezo in vedenjsko simulacijo

- Preden zaženete vedenjsko simulacijo, zaženite sintezo in se prepričajte, da v datoteki testbench in enoti v preskusni datoteki ni nobenih sintaktičnih napak

- Zaženite vedenjsko simulacijo

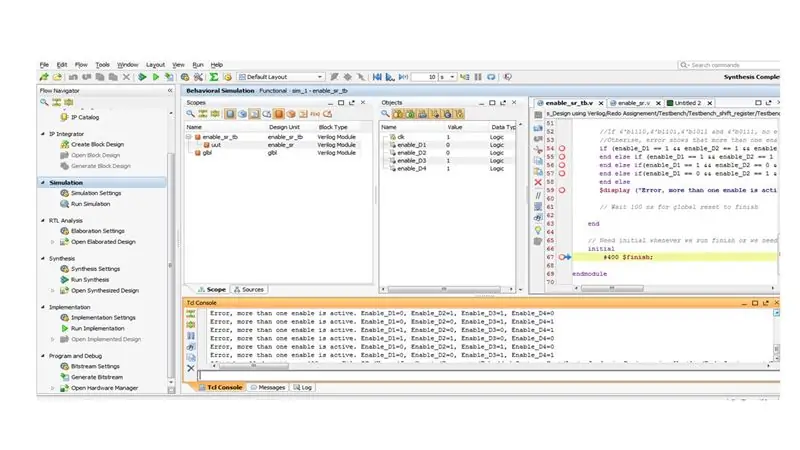

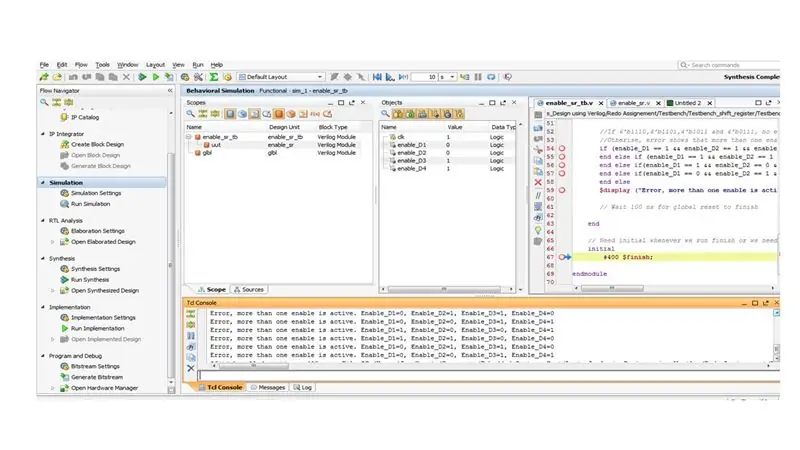

Korak 6: Ocenite rezultat simulacije

Videli boste okna za simulacijo. Vsebuje različne plošče.

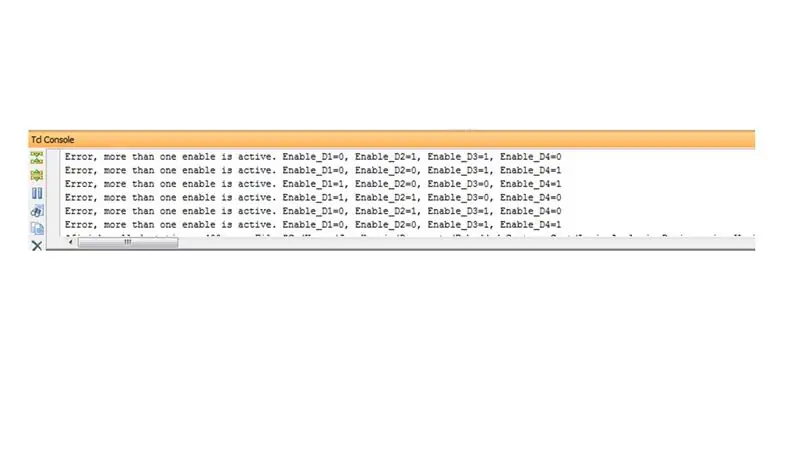

Sporočilo o napaki se prikaže na plošči konzole. To kaže, da je v obdobju simulacije aktivnih več kot ena številka.

V obsegu si lahko ogledate tudi valovno obliko

Priložena je projektna datoteka.

Priporočena:

Arduino Kako uporabljati 1,3 -palčni OLED zaslon SH1106: 7 korakov

Arduino Kako uporabljati 1,3 -palčni OLED zaslon SH1106: V tej vadnici se bomo naučili, kako uporabljati 1,3 -palčni OLED zaslon SH1106 Arduino in Visuino programsko opremo. Oglejte si video

Kako ustvariti zagonski pogon Linuxa (in kako ga uporabljati): 10 korakov

Kako ustvariti zagonski pogon Linuxa (in kako ga uporabljati): To je preprost uvod o tem, kako začeti z Linuxom, zlasti Ubuntu

Rotacijski dajalnik: Kako deluje in kako uporabljati z Arduinom: 7 korakov

Rotacijski dajalnik: Kako deluje in kako ga uporabljati z Arduinom: To in druge neverjetne vaje lahko preberete na uradni spletni strani ElectroPeak Pregled V tej vadnici boste spoznali, kako uporabljati rotacijski kodirnik. Najprej boste videli nekaj informacij o rotacijskem kodirniku, nato pa se boste naučili, kako

Kako uporabljati Mac Terminal in kako uporabljati ključne funkcije: 4 koraki

Kako uporabljati Mac Terminal in kako uporabljati ključne funkcije: Pokazali vam bomo, kako odpreti terminal MAC. Prikazali vam bomo tudi nekaj funkcij v terminalu, na primer ifconfig, spreminjanje imenikov, dostop do datotek in arp. Ifconfig vam bo omogočil preverjanje vašega naslova IP in vašega oglasa MAC

Kako uporabljati Wiimote kot računalniško miško in uporabljati sveče kot senzor !!: 3 koraki

Kako uporabljati Wiimote kot računalniško miško in uporabljati sveče kot senzor !!: Ta priročnik vam bo pokazal, kako povezati daljinski upravljalnik Wii (Wiimote) z računalnikom in ga uporabiti kot miško